エスケーハイニックス株式会社により出願された特許

1 - 10 / 122

半導体装置及び半導体装置の動作方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

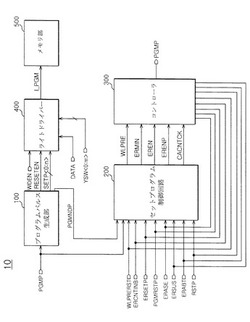

半導体メモリ装置、このためのセットプログラム制御回路及びプログラム方法

【課題】消去命令に応答してセットデータをプログラムできる半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法を提供する。

【解決手段】本発明に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、消去命令に応答して第1書き込み制御信号をディスエーブルし、セットプログラミングイネーブル信号に応答してプログラミングイネーブル信号を生成するコントローラとを含むことができる。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体メモリ装置

【課題】本発明は、リフレッシュ動作の時、電流消耗を減らすことができる半導体メモリ装置を提供する。

【解決手段】第1ビットライン分離信号に応答してビットラインとセンスアンプとを連結及び分離させる第1スイッチと、第2ビットライン分離信号に応答してビットラインバーとセンスアンプとを連結させる第2スイッチと、及びリフレッシュ動作の時、第2ビットライン分離信号のイネーブル区間の長さよりイネーブル区間が短いリフレッシュ用ビットライン分離信号を生成して第2スイッチに提供する制御部を備える。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置及びこれを備える半導体システム並びにその動作方法

【課題】内部でデータ基準電圧を生成する半導体装置を提供すること。

【解決手段】本発明の半導体装置は、設定されたデータパターンを有する比較データを外部から印加されて設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分して格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、外部から印加されるレベルテストコードに応答してその電圧レベルが決定されるデータ基準電圧のレベルに基づいて、設定された時間ごとに前記設定されたデータパターンを有する状態で外部から印加されるテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較してテスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、を備える。

(もっと読む)

アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

(もっと読む)

半導体メモリ装置、半導体メモリ装置のための分割プログラム制御回路及びプログラム方法

【課題】本発明の実施形態はメモリ領域を分割してプログラムできる半導体メモリ装置と、このための分割プログラム制御回路及びプログラム方法を提供することにある。

【解決手段】本発明による半導体メモリ装置はプログラミングイネーブル信号に応答して書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、プログラム完了信号に応答して既設定されたプログラム分割回数によって分割プログラミングイネーブル信号を生成する分割プログラム制御回路及び分割プログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラを含むことができる。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

1 - 10 / 122

[ Back to top ]