エスケーハイニックス株式会社により出願された特許

41 - 50 / 122

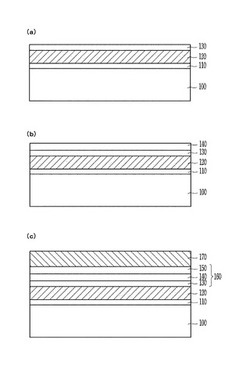

半導体素子の製造方法

【課題】400℃以上の温度で原子層蒸着法により蒸着が可能な前駆体を用いて高密度を有する非晶質の高誘電絶縁膜形成を通じてキャパシタンス等価厚及び漏洩電流特性を向上させることができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にZr[C5H4(CH3)]2(CH3)2、Zr[C5H4(CH3)]2(OCH3)CH3及びZr[C5H4(CH2CH3)][N(CH3)(CH2CH3)]3の何れか一つの前駆体を用いて400℃〜500℃の温度で形成されたジルコニウム酸化膜(ZrO2)140を含む高誘電絶縁膜を形成することを特徴とする。

(もっと読む)

半導体パッケージ、これを有する積層ウエハーレベルパッケージおよび積層ウエハーレベルパッケージの製造方法

【課題】複数個のウエハーレベルパッケージを積層して、データ保存容量およびデータ処理速度を向上させる製造方法を提供する。

【解決手段】ボンディングパッド224を有する半導体チップ220と、半導体チップ220の外郭を覆って、ボンディングパッド224を露出する第1絶縁膜パターン230と、第1絶縁膜パターン230上に配置され、各ボンディングパッドから半導体チップ220の外部まで延び、半導体チップ220の外部から第1絶縁膜パターン230を貫く連結パターン246を有する再配線パターン240と、第1絶縁膜パターン230上に配置され、再配線パターン240の一部を露出する開口を有する第2絶縁膜パターン250とを含む。

(もっと読む)

モールド再構成ウェハーを利用したスタックパッケージ及びその製造方法

【課題】 製造工程が簡単で製造費用を抑えることができるモールド再構成ウェハーを利用したスタックパッケージ及びその製造方法を提供する。

【解決手段】 少なくとも二つ以上のパッケージユニットがスタックされたスタックパッケージにおいて、前記パッケージユニットは、上面にボンディングパッドを具備した半導体チップと、前記半導体チップの側面を取り囲むように形成されたモールド部と、前記モールド部内に形成された貫通電極と、前記貫通電極とこれに隣接したボンディングパッドとを相互連結させるように形成された再配線とを含み、前記貫通電極と再配線とが、一体的に形成されている。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】半導体基板のセル領域と周辺回路領域との間に段差をなくして、工程を容易かつ単純にしつつ、特に、コンタクトナットオープン(Contact not open)、下部構造物に対するアタック(Attack)などを防止し、工程歩留まり及び信頼性を向上させることができる不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】周辺回路領域及び該周辺回路領域より高さが低いセル領域を有する半導体基板と、該半導体基板の前記セル領域上に配置され、複数の層間絶縁膜及び複数の制御ゲート電極が交互に積層された制御ゲート構造物と、該制御ゲート構造物が形成された前記半導体基板の前記セル領域を覆う第1の絶縁膜と、該第1の絶縁膜上の選択ゲート電極と、前記半導体基板の前記周辺回路領域上の周辺回路素子とを備えることを特徴とする。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

ヒューズ回路を含む半導体集積回路および半導体メモリ装置

【課題】ヒューズ回路を構成する回路素子数の増加を最小化しつつ、ヒューズを再接続する金属イオンの電気/化学的マイグレーション現象を防止することができる半導体集積回路を提供する。

【解決方法】ヒューズFUSEと、第1ヒューズ感知信号INに応答して感知ノードAを第1駆動する第1駆動部20と、ヒューズFUSEとともに駆動経路を構成し、第2ヒューズ感知信号IN2に応答して感知ノードAを第2駆動する第2駆動部22と、ヒューズFUSEと並列に接続されたバイパス抵抗部24と、感知ノードAの電圧に応答してヒューズFUSEのプログラミング状態を感知する感知部26とを備える半導体集積回路が提供される。

(もっと読む)

回路配線を有する回路基板の製造方法、ならびに回路配線を有する半導体パッケージ

【課題】製造工程が単純で、製造工程中における不良確認が可能であり、同一平面上で相互交差できる回路配線を有する回路基板を提供する。

【解決手段】第1の端子15および前記第1の端子と離隔された第2の端子18を有する基板本体10と、それぞれ第1の極性および前記第1の極性と反対の第2の極性を有する導電性分極パーティクル22を前記基板本体上に連続的に配置して、前記第1および第2の端子を電気的に連結する配線部22と前記配線部を覆う絶縁部24とを含む配線20とを含む回路基板100を製造する。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】リペア過程が簡素化された半導体メモリ装置及びそのリペア方法を提供する

【解決手段】半導体メモリ装置200は、複数のメモリセルを含む第1のメモリチップないし第3のメモリチップ210〜230と、第1のリペアチップ240とを備え、第1のリペアチップ240は、第1のメモリチップないし第3のメモリチップ210〜230のそれぞれに含まれた複数のメモリセル212A,212B,・・・のうち、欠陥が発生した任意のメモリセルをリペアするための第1のヒューズ回路ないし第3のヒューズ回路241A,241B,243A,243B,245A,245Bと、メモリチップ210〜230毎に欠陥が発生した任意のメモリセルを代替するための、複数の第1のリダンダンシメモリセルないし第3のリダンダンシメモリセル242A,242B,244A,244B,246A,246Bとを含む。

(もっと読む)

デジタルカメラ装置における画像処理装置及び方法

【課題】デジタルカメラで撮像された画像の明るさを処理するための装置及び方法を提供する。

【解決手段】デジタルカメラの画像処理装置であって、レンズ101から受信された光学情報をCIS(CMOS Image Sensor or Contact Image Sensor)素子103によって画像情報として処理する画像信号収集部101〜107,109と、画像信号収集部で収集された情報に対応する補償カーブに応じてルミナンス値を補償し、ルミナンス値に応じて補償された画像信号を出力する画像補正部110とを備える。

(もっと読む)

41 - 50 / 122

[ Back to top ]