Fターム[5F082AA35]の内容

Fターム[5F082AA35]の下位に属するFターム

クロストーク防止 (15)

Fターム[5F082AA35]に分類される特許

1 - 6 / 6

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】外部からの高周波ノイズに対して誤動作しにくい半導体装置およびその製造方法を提供する。

【解決手段】n型コレクタ層11上に配置されたp型ベース層12bと、p型ベース層12b上に配置されたn型エミッタ層13bと、p型ベース層12b上にp型ベース層12bを包囲するように配置されたn型ベースコンタクト層21と、n型コレクタ層11上にp型ベース層12bと離隔して配置されたp型アノード層12cと、n型エミッタ層13bに接続されたエミッタ電極16cと、p型ベース層12bおよびn型ベースコンタクト層21に接続されたベース電極16aと、p型アノード層12cに接続され、かつエミッタ電極16cと共通接続されたアノード電極16bと、エミッタ電極16cとベース電極16a間に接続された第1抵抗R1と、ベース電極16aに接続された第2抵抗R2とを備える。

(もっと読む)

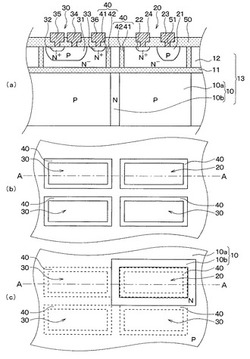

半導体装置

【課題】複数の回路を搭載する場合において、回路間のノイズ伝播などの誤動作を抑制することが可能な半導体装置を提供すること。

【解決手段】支持基板と、前記支持基板上に設けられた絶縁層と、前記絶縁層上に設けられ第1回路を有する第1半導体層と、前記絶縁層上に設けられ、前記第1半導体層と絶縁され、第2回路を有する第2半導体層と、前記絶縁層上のうち前記第1半導体層と前記第2半導体層との間に設けられ、前記第1半導体層及び前記第2半導体層とそれぞれ絶縁され、電気的に接地された容量領域を有する分離層とを備える。

(もっと読む)

モータ駆動回路、ファンモータ、電子機器、及びノート型パーソナルコンピュータ

【課題】異常動作の発生を抑制することを可能にする。

【解決手段】モータ駆動回路は、入力電極が電源側に接続され出力電極がモータコイルの一端と接続される第1トランジスタと、入力電極がモータコイルの一端と接続され出力電極が接地側に接続される第2トランジスタと、入力電極が電源側に接続され出力電極がモータコイルの他端と接続される第3トランジスタと、入力電極がモータコイルの他端と接続され出力電極が接地側に接続される第4トランジスタと、第1及び第4トランジスタがオンの状態と第1〜第4トランジスタ全てがオフの状態とを適宜選択してモータコイルを駆動する駆動制御回路と、入力電極が電源側に接続され出力電極がモータコイルの一端と接続された第5トランジスタと、第5トランジスタがオンになると第4トランジスタをオンさせる保護回路とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体集積回路

【課題】トランジスタのN型領域が負電位となる半導体集積回路において、寄生電流の影響を効果的に防止できるとともに、チップ面積の増大を防ぐことができる半導体集積回路を提供することを目的とする。

【解決手段】N領域が負電位となるトランジスタQ1と、そのトランジスタQ1に隣接するトランジスタQ2との間のP型分離領域12中に、N型島領域としてのコンタクト領域11を電源電位とした抵抗領域のP型領域10を配置する。また、P型分離領域12をトランジスタQ1の周囲を取り囲むように配置し、さらにコンタクト領域11を、トランジスタQ1の外側を取り巻くように配置することにより、チップ面積の増加を伴わずに、寄生トランジスタQ3,Q4による影響を低減する。

(もっと読む)

1 - 6 / 6

[ Back to top ]