Fターム[5F082EA25]の内容

Fターム[5F082EA25]に分類される特許

1 - 20 / 31

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

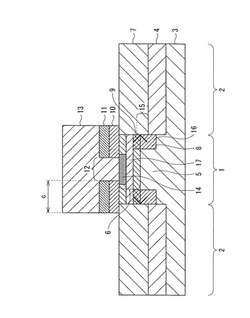

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの特性が劣化するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域A上にプレーナ型のバイポーラトランジスタ1を形成する工程と、プレーナ型バイポーラトランジスタ1が形成される領域を覆うようにシリコン窒化膜からなるカバー膜32aを形成する工程と、その後、プレーナ型のバイポーラトランジスタ1が形成される領域Aがカバー膜32aに覆われた状態で、バイポーラトランジスタ1が形成される領域にイオン注入する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド化の工程をMOSトランジスタ及びHBTと別けることなく、抵抗値のばらつきが小さいヒューズ素子を形成する半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、MOSトランジスタ形成領域11Bにゲート電極22及びソースドレイン領域25を形成する工程と、MOSトランジスタ形成領域11Bを除いて、半導体基板11の上にシリコン及びシリコン以外のIV族元素を含む混晶膜と、シリコン膜とが順次積層された積層膜31A、31Bを形成する工程と、シリコン膜30Bの露出部分、ゲート電極22の上部及びソースドレイン領域25の上部をシリサイド化する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく高速バイポーラトランジスタと高耐圧バイポーラトランジスタを同一半導体基板上に形成し、高耐圧バイポーラトランジスタを使用する回路の歪特性を低減できる半導体装置の製造方法の提供。

【解決手段】半導体基板101上に、コレクタの一部となる埋込み領域102を、第1、第2のバイポーラトランジスタの形成領域に同一工程で形成し、エピタキシャル層104を形成し、第1の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の全体に形成し、第2の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の1箇所に埋込み領域を形成しない領域を有して形成する。第2の縦型バイポーラトランジスタの埋込み領域を形成しない領域では、周囲からの不純物の拡散により、縦方向の拡散拡がり量が連続的に狭くなり、埋込み領域を形成しない領域が形成される。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、電極の側方に形成された異種の材料からなる複合膜の残渣の除去を容易に行うことが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、シリコン基板11の電界効果型トランジスタが形成される領域B上にゲート電極を形成する工程と、シリコン基板11のバイポーラトランジスタが形成される領域A上にバイポーラトランジスタを構成するSiGeからなるエピタキシャル層19aを形成する工程と、エピタキシャル層19aの形成時にゲート電極の側方に形成されるSiGeおよび多結晶シリコンからなるエッチング残渣19c、25bおよび43aを除去する工程と、その後、ゲート電極の側方を覆うサイドウォール絶縁膜と、エミッタ電極25の側方を覆うサイドウォール絶縁膜とを形成する工程とを備える。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの所望の特性が出なくなるのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、バイポーラトランジスタ1と、素子分離絶縁膜17および素子分離絶縁膜16と、ベース・コレクタ間分離絶縁膜18とを備えている。また、ベース・コレクタ間分離絶縁膜18と素子分離絶縁膜16との間に埋込コレクタ領域12のリーチスルー領域12aが配置されており、ベース電極20および21は、それぞれ、ベース・コレクタ間分離絶縁膜18および素子分離絶縁膜17に乗り上げるように配置されており、素子分離絶縁膜17のベース電極20が乗り上げている部分およびベース・コレクタ間分離絶縁膜18のベース電極21が乗り上げている部分の厚みは、バイポーラトランジスタ1が形成される領域以外の領域に形成される素子分離絶縁膜16の厚みよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部の製造工程が増加するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この発明の半導体装置100の製造方法は、半導体基板11を準備する工程と、互いに隣接する素子領域間に素子分離絶縁膜12を形成する工程と、半導体基板11の電界効果型トランジスタ2が形成される領域Bと、互いに隣接する素子領域間に配置される素子分離領域Cとに不純物を導入することにより、電界効果型トランジスタ2が形成される領域Bを覆うpウェル22と、素子分離領域Cの素子分離絶縁膜12の下面に接触するように配置されるpウェル28とを同時に形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、第1素子のゲート電極および第2素子の電極部のそれぞれの側面を覆うサイドウォール絶縁膜の幅を異ならせることが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域B上にゲート電極28を形成する工程と、シリコン基板11の領域Aにスペーサ絶縁膜42を、ゲート電極28の側面および領域Aを覆うように形成することにより、領域Aを覆う保護膜と、ゲート電極28の側面を覆う絶縁膜42aを形成する工程と、その後、領域A上にエミッタ電極25を形成する工程と、ゲート電極28およびエミッタ電極25を覆うようにシリコン酸化膜49を形成する工程と、スペーサ絶縁膜42およびシリコン酸化膜49をエッチングすることにより、絶縁膜42aを覆う絶縁膜30aを形成するとともに、エミッタ電極25の側面を覆うサイドウォール絶縁膜26を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、低温下で結晶性の良好な単結晶および多結晶を提供することを目的とする。また、本発明は、固相成長法を用い、信頼性の高い半導体装置を提供することを目的とする。

【解決手段】

本発明では、非晶質半導体薄膜を基板あるいは絶縁膜上に堆積するにあたり、特に、その膜を構成する主元素からなる非晶質膜の平均原子間隔分布が、単結晶の平均原子間隔分布にほぼ一致するように形成し、これに再結晶化エネルギーを付与し固相成長を行い単結晶半導体薄膜3を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の第2素子が形成される領域にエッチングによるダメージが発生するのを抑制しながら第1素子のゲート電極の側面を覆うサイドウォール絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の電界効果型トランジスタ2が形成される領域にゲート電極28を形成する工程と、ゲート電極28の表面およびシリコン基板11のバイポーラトランジスタ1が形成される領域を覆うようにスペーサ絶縁膜42を形成する工程と、スペーサ絶縁膜42を表面から所定の厚み分エッチングすることにより、シリコン基板11のバイポーラトランジスタ1が形成される領域にスペーサ絶縁膜42を所定の厚み分残した状態でゲート電極28の側面を覆うサイドウォール絶縁膜30を形成する工程とを備える。

(もっと読む)

BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタ

【課題】BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタを提供する。

【解決手段】隆起した外因性自己整合型ベースを有する高性能バイポーラ・トランジスタが、CMOSデバイスを含むBiCMOS構造と統合される。パッド層を形成して、先在するCMOSデバイスのソースおよびドレインに対して真性ベース層の高さを隆起させることにより、かつ選択的エピタキシを介して外因性ベースを形成することにより、表面の凹凸の影響は、外因性ベースのリソグラフィによるパターン形成時に最小になる。また、バイポーラ構造の製作の間に、化学機械研磨プロセスを使用しないことにより、プロセス統合の複雑さが軽減される。内側のスペーサまたは外側のスペーサが、エミッタからベースを分離するために形成されうる。パッド層、真性ベース層、および外因性ベース層は、一致した外側の側壁表面を有するメサ構造を形成する。

(もっと読む)

接合型電界効果トランジスタ及びその製造方法及び半導体装置

【課題】コレクタエピタキシャル層を薄膜化した高速バイポーラトランジスタを搭載した集積回路中に所望の高耐圧J−FETを混載可能とした半導体装置及びその製法を提供すること。

【解決手段】P型の単結晶Si基体などの第1導電型の半導体基体2上にシリコン半導体層などの第2導電型の半導体層3を積層し、この半導体層3中にAs(ヒ素)等の第2導電型の不純物によってソース領域12及びドレイン領域13を形成し、さらにこの半導体層3上に、シリコン・ゲルマニウム層によってP型の第1導電型不純物(例えば、ホウ素など)を有するゲート領域14を形成する。

(もっと読む)

半導体装置

【課題】正孔の移動を十分に抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置(npn型のバイポーラトランジスタ100)は、n型コレクタ層2と、p+拡散層4、SiGe層5およびp型シリコン膜6からなるベース層と、n型エミッタ層8と、n型コレクタ層2とn型エミッタ層8との間に形成され、電子または正孔のいずれか一方に対する電位障壁としての効果を有する電荷移動防止膜7とを備える。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増やすことなく、バイポーラ領域内でのサイドウォールの残存やサブトレンチの形成を防止できるようにした半導体装置の製造方法を提供する。

【解決手段】SiGe−HBT50とCMOSとを同一基板1上に形成する半導体装置の製造方法であって、バイポーラ領域とCMOS領域とを素子分離するDTI13及びLOCOS層15Aを基板1に形成する工程と、CMOSのゲート電極の材料膜であるポリシリコン膜22を基板1上の全面に形成する工程と、このポリシリコン膜をパターニングして、CMOS領域の基板1上にゲート電極を形成する工程とを含み、ゲート電極を形成する工程では、バイポーラ領域上から当該領域周辺のLOCOS層15A上までを全て覆うようにポリシリコン膜22を基板1上に残存させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】金属膜を必要以上に薄く形成しなくても、LOCOSエッジ付近での金属膜とベース絶縁膜との過度な合金化を防止できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】エミッタ領域の基板1上からLOCOS層15B上にかけてシリコンゲルマニウム層51を連続して形成する。次に、エミッタ59領域のシリコンゲルマニウム層51上にエミッタ59を形成する。そして、エミッタ59が形成された基板1上にシリコン酸化膜を形成し、次に当該シリコン酸化膜をエッチバックすることによって、エミッタ59の側面にサイドウォール61Aを形成する。その後、基板1上にTiを形成し熱処理を施して、チタンシリサイド膜67を形成する。サイドウォール61Aを形成する工程では、LOCOSエッジ90上にサイドウォール61Bを付随的に形成する。

(もっと読む)

半導体デバイスの製造方法及び当該方法により得られる半導体デバイス

本発明は、基板(11)と、エミッタ領域(1)、ベース領域(2)及びコレクタ領域(3)を有する少なくとも1つのバイポーラトランジスタを備える半導体本体(12)とを有する半導体デバイス(10)の製造方法であって、当該半導体本体(12)に、前記コレクタ領域とエミッタ領域(1、3)のうちの一方の領域(3)を形成する第1の半導体領域(13)を形成し、半導体本体(12)の表面上には、第1の絶縁層(4)、多結晶半導体層(5)及び第2の絶縁層(6)から成る層のスタックを形成し、該スタックに開口(7)を形成し、その後に、非選択的エピタキシャル成長によって、更なる半導体層(22)を堆積し、開口(7)の底面上の単結晶の水平部分がベース領域(2)を形成し、開口(7)の側面上の多結晶の垂直部分(2A)は多結晶半導体層(5)に接続し、その後に、開口(7)の側面に平行にスペーサ(S)を形成し、そしてエミッタ及びコレクタ領域(1、3)のうちの他方の領域(1)を形成する第2の半導体領域(31)を前記スペーサ(S)の間に形成する、半導体デバイスの製造方法に関する。本発明によれば、上記方法は、前記更なる半導体層(22)を堆積する前に、前記第2の絶縁層(6)に、その下に在る半導体層(5)の端部(5A)から張り出して突出して見える端部(6A)を設けることを特徴とする。この方法により、費用効率の高い、良好な高周波特性を有するバイポーラトランジスタデバイスを得ることができる。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

本発明は、シリコンからなる基板(11)および半導体本体(12)を有し、この半導体本体(12)は、トランジスタ(T)を有する能動領域(A)および該能動領域(A)を囲む受動領域(P)を具え、前記半導体本体(12)の表面から埋め込まれた金属材料からなる第1導電領域(2)に接続している金属材料からなる第2導電領域(1)が設けられ、これによって、前記第2導電領域(1)が、前記半導体本体(12)の表面で電気的に接続可能とされる半導体デバイス(10)に関するものである。本発明によれば、前記第2導電領域(1)は、前記半導体本体(12)の能動領域(A)の場所で作られる。このような方法で、非常に低い埋込抵抗は、前記周囲のシリコンとは完全に異なる結晶特性を有する金属材料を用いて、前記半導体本体(12)の能動領域(A)の中で局所的に生成されることができる。これは、本発明に従う方法を用いることによって可能となる。そのような埋込低抵抗は、バイポーラトランジスタおよびMOSトランジスタの双方にとって多くの利点を提案する。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]