Fターム[5F083AD53]の内容

Fターム[5F083AD53]に分類される特許

21 - 34 / 34

半導体装置及びその製造方法

【課題】キャパシタを有する信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の絶縁膜26と、ソース/ドレイン拡散層22に達する第1のコンタクトホール28a内に埋め込まれた第1の導体プラグ32と、第1の絶縁膜上に形成されたキャパシタ44と、第1の絶縁膜上に、キャパシタを覆うように形成された第1の水素拡散防止膜48と、第1の水素拡散防止膜上に形成され、表面が平坦化された第2の絶縁膜50と、第2の絶縁膜上に形成された第2の水素拡散防止膜52と、キャパシタの下部電極38又は上部電極42に達する第2のコンタクトホール56内に埋め込まれた第2の導体プラグ62と、第1の導体プラグに達する第3のコンタクトホール内に埋め込まれた第3の導体プラグ62と、第2の導体プラグ又は第3の導体プラグに接続された配線64とを有している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】簡便な方法により、マスク側壁への反応生成物の堆積を防止することができる半導体装置を製造する方法を提供する。

【解決手段】下部電極21、強誘電体、常誘電体、反強誘電体等による誘電体層22、及び上部電極23を含むキャパシタを複数備える半導体装置の製造方法は、上部電極層をパターニングして、複数の上部電極23、23’、23”を形成する工程と、複数の上部電極23、23”を被覆し、かつ最端に配置された上部電極23’の少なくとも一方側の端部を露出する第1マスクパターンを形成する工程と、第1マスクパターンを用いて、誘電体層22をパターニングする工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】シリンダ孔の側面が外側に膨らむ現象(ボーイング)をより抑制して、高アスペクト比の深孔を形成できると共に、深孔の外抜き工程で電極が倒壊しないDRAM等の半導体装置の製造方法を提供する。

【解決手段】半導体基板11の表面部分に拡散層を形成し、その上部に第1絶縁膜13,17を形成する工程と、第1絶縁膜13,17を貫通し、拡散層以外の半導体基板11の表面部分及び拡散層の表面部分にそれぞれ接する放電プラグ22及び導体プラグ15,18を形成する工程と、第1絶縁膜17、放電プラグ22及び導体プラグ18を覆う導電性を有するアモルファスカーボン等の炭素含有膜23を形成する工程と、炭素含有膜23を貫通し、導体プラグ18に接する第1導電膜29を形成する工程と、炭素含有膜23を除去して第1導電膜29を露出させる工程と、有する。

(もっと読む)

セラミックス膜およびその製造方法ならびに半導体装置、圧電素子およびアクチュエータ

【課題】セラミックス膜の表面モフォロジを改善することができる、セラミックス膜の製造方法を提供する。このセラミックス膜の製造方法により得られたセラミックス膜を提供する。このセラミックス膜が適用された半導体装置および圧電素子を提供する。

【解決手段】セラミックス膜の製造方法は、原材料体20を結晶化することにより、セラミックス膜30を形成する工程を含み、原材料体20は、種類が異なる原料を混在した状態で含み、種類が異なる原料同士は、原料の結晶化における結晶成長条件および結晶成長機構の少なくとも一方が相互に異なる関係にある。

(もっと読む)

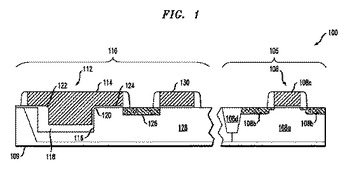

ランダム・アクセス・メモリ・デバイスのトレンチ・キャパシタ漏洩電流を低減する方法

本発明は、一態様では、半導体デバイスを製造する方法を提供する。この方法は、半導体基板(109)のダイナミック・ランダム・メモリ領域(DRAM)(110)内にトレンチ分離構造(118)を形成すること、ならびにトレンチ分離構造(118)の上に、トレンチ分離構造(118)の一部分を露出するようにエッチング・マスクをパターニングすることを含む。露出したトレンチ分離構造(118)の一部分を除去してその中に、半導体基板によって形成された第1の角部と、トレンチ分離構造によって形成された第2の角部とを含むゲート・トレンチ(116)を形成する。エッチング・マスクをDRAM領域(110)から除去し、ゲート・トレンチの少なくとも第1の角部に丸みをつけて、丸みをつけた角部(120)を形成する。この後に、ゲート・トレンチ(116)の側壁の上、第1の丸みをつけた角部(120)の上、およびゲート・トレンチ(116)に隣接する半導体基板(109)の上の酸化物層(124)の形成を続ける。トレンチ(116)をゲート材料で充填する。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体記憶装置

【課題】通常のCMOSプロセスにおいてDRAMを作製でき、低い製造コストで製造可能なDRAMの混載した半導体記憶装置を提供する。

【解決手段】半導体基板上に形成された第1及び第2のトランジスタT1、T2と、セルデータ電荷を保持するための2つのノードSNt、SNcと、周囲に形成されたシールド電極により構成される1ビットのメモリセル11領域であって、各々のノードSNt、SNcは第1、第2のトランジスタT1、T2のドレインに接続されており、第1及び第2のトランジスタT1、T2のゲートはともに同一のワード線WL0に接続されており、第1及び第2のトランジスタT1、T2のソースは第1、第2のビット線BLt0、BLc0に接続され、第1及び第2のビット線BLt0、BLc0は、同一のセンスアンプSA12に接続され、1ビットのメモリセル領域が2次元的にアレイ状に形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 半導体記憶装置及びその製造方法に関し、特に、電源を切っても記憶情報を保持しうる不揮発性を有し、情報の保持能力や耐久性などの信頼性が高く、集積度が高くビット単価が安い半導体記憶装置を提供する。

【解決手段】 ゲートGがワード線WLに接続され、一方のソース/ドレインS/Dがビット線BLに接続された転送トランジスタTrと、転送トランジスタTrの他方のソース/ドレインS/Dに一方の電極が接続され、常誘電体を誘電体膜とする常誘電体キャパシタC1と、転送トランジスタTrの他方のソース/ドレインS/Dに一方の電極が接続され、強誘電体を誘電体膜とする強誘電体キャパシタC2とにより半導体記憶装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 誘電体膜に用いる材料及び容量上部電極に用いる材料に依存することなく、上部電極のセルプレートの配線遅延を防止し、高集積で且つ高速動作が可能な立体スタック型構造の誘電体メモリを提供する。

【解決手段】 半導体装置は、半導体基板(10)上に形成された第1の凹部(15a)を有する絶縁膜(14)と、第1の凹部(15a)の壁部及び底部に形成された第2の凹部(15b)を有する容量下部電極(16)、第2の凹部(15b)の壁部及び底部に形成された第3の凹部(15c)を有する誘電体膜よりなる容量絶縁膜(17)、並びに第3の凹部(15c)の壁部及び底部に形成された容量上部電極(18A)からなる複数の容量素子とを備える。複数の容量素子を構成する容量上部電極(18A)の少なくとも一部を被覆し、且つ、複数の容量素子に跨るように形成された、容量上部電極(18A)の抵抗よりも低い抵抗を有する低抵抗導電層(19A)を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 キャパシタ形成後のコンタクトプラグ形成時又は配線層形成時等に容量絶縁膜に加わるプラズマダメージを低減することにより、容量絶縁膜の劣化を抑制してキャパシタリーク電流の増大を防止する。

【解決手段】 半導体基板100上の第1の層間絶縁膜106の上に形成され第2の層間絶縁膜109に、キャパシタ領域となる凹部110が形成されている。凹部110内に下部電極(第2のポリシリコン膜412及びHSG膜413)が形成されていると共に該下部電極上に容量絶縁膜となる酸化タンタル膜115及び上部電極となる第1の窒化チタン膜が形成されている。当該上部電極及び上層配線124のそれぞれと接続するプレートコンタクト120が、第1の層間絶縁膜106中に形成されたプラグ107Cを介して、半導体基板100の表面部のN型不純物拡散層105と電気的に接続されている。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置及びこの装置の信号ライン配置方法を提供する。

【解決手段】サブワードラインとビットライン対との間に接続されるメモリセルを備えたサブメモリセルアレイを備え、ビットライン対とローカルデータラインLIO対、グローバルデータラインGIO対との間にデータを伝送するメモリセルアレイ、及びメモリセルアレイを全体的に覆ってメモリセルに必要な電圧を印加する電極を備えて、ローカルデータラインLIO対が電極の上部の1層にサブワードラインと同じ方向に配置され、コラム選択信号ラインCSL及びグローバルデータラインGIO対が電極の上部の第2層にビットラインと同じ方向に配置され、ワード選択信号ライン及びメインワードラインNWLiが電極の上部の第3層にサブワードラインと同じ方向に配置される。これによって、電極からワードラインに流れる漏洩電流が防げられて電極の電圧レベルの降下を防止できる。

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

半導体記憶装置

【課題】 1交点方式(オープンビット線型)のダイナミック型RAMにおいて、隣接するビット線間に生じる干渉ノイズを有効に減少させる。

【解決手段】 センスアンプ列7を中心に左右にサブアレイ8、8が配置される。この各サブアレイは多数のダイナミック型メモリセルMC…を有する。センスアンプ列7の左方及び右方に位置するサブアレイ8、8において、同一行のビット線同士(BL0、NBL0)〜(BLn、NBLn)により相補のビット線対が構成されていて、オープンビット線型となっている。各サブアレイ8、8において、各ビット線BL0〜BLn、NBL0〜NBLn間には、各々、これらのビット線と平行に且つ同一配線層に形成された第1の配線パターンSLDが配置される。これらの配線パターンSLDは全て電源電位などの固定電位に設定される。

(もっと読む)

21 - 34 / 34

[ Back to top ]