Fターム[5F083JA04]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564) | シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA04]に分類される特許

1,941 - 1,945 / 1,945

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

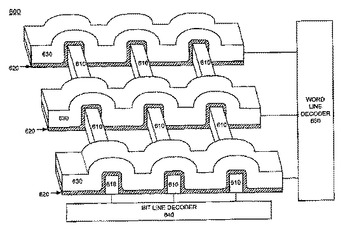

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】下層のポリシリコン膜を酸化させることなく、酸素アニールによりHTO膜を十分に改質させ、電気的にリークが少ないトンネル酸化膜を形成する半導体装置の製造方法を提供すること。

【解決手段】ポリシリコン膜からなる第1フローティングゲート16上に、窒化膜26又は酸窒化膜28を介してHTO膜を成膜し、酸素アニール処理を施して、トンネル酸化膜18(HTO膜)を形成する。

(もっと読む)

半導体装置および半導体記憶装置

【課題】本発明は、素子間分離にSTI構造を採用する不揮発性半導体記憶装置において、ソース領域をより確実に接続できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、P型シリコン基板11の表面部に、浅い第一の埋め込み素子分離絶縁膜22と、この第一の埋め込み素子分離絶縁膜22よりも深い、第二の埋め込み素子分離絶縁膜23とからなる素子分離領域24を形成する。そして、第一の埋め込み素子分離絶縁膜22を除去した後に、その底部とメモリセルトランジスタのソース領域とに不純物をイオン注入する。こうして、第一の埋め込み素子分離絶縁膜22のアスペクト比を下げ、トレンチ溝の側壁部分に対しても十分に拡散層を形成できるようにすることで、ソース線SLとなる、連続したN+ 型ソース領域19の形成を可能とする構成となっている。

(もっと読む)

1,941 - 1,945 / 1,945

[ Back to top ]