Fターム[5F083JA46]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 酸化物導電体 (2,345) | 複酸化物 (752) | 層状化合物 (12)

Fターム[5F083JA46]に分類される特許

1 - 12 / 12

半導体装置及びその製造方法

【課題】所望の特性を維持しつつ強誘電体膜のより一層の薄膜化が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された強誘電体キャパシタ62は、下部電極48と、強誘電体特性を備えた誘電体膜(強誘電体膜)50と、上部電極60とを有する。上部電極50は、Ir等の導電材料を添加して導電性を付与した強誘電体材料により形成された導電体酸化物膜52を備え、この導電体酸化物膜52が誘電体膜50に接している。これにより、誘電体膜50と上部電極膜60との間に常誘電体層が発生することが抑制され、所望の特性を維持しつつ誘電体膜50のより一層の薄膜化が可能になる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を薄膜化して低電圧の動作を可能にしつつ、飽和反転電荷量を増大ささせる。

【解決手段】半導体装置は、下部電極41と、強誘電体膜36と、上部電極35とから形成されるキャパシタ42を有する。強誘電体膜36は、PZTから形成され、膜厚方向の中央部分のTiの含有量が他の領域の比べて多くなっている。Tiの分布は、膜厚方向の中央から上下の電極35,41に向けて減少するような分布である。さらに、Srなどのドーパント元素の含有量が、下部電極41との界面で最も多く、上部電極35に向けて減少する分布を有する。

(もっと読む)

圧電体膜の成膜方法、圧電素子、液体吐出装置、及び圧電型超音波振動子

【課題】圧電特性及び駆動耐久性の良好な鉛含有ペロブスカイト型酸化物からなる圧電体膜を簡易な方法により成膜する。

【解決手段】本発明の鉛含有ペロブスカイト型酸化物からなる圧電体膜の成膜方法は、スパッタリング法による成膜において、成膜途中で、前記基板の電位を第1の基板電位Vsub1から、前記圧電体膜の鉛組成を所望の組成とするように第2の基板電位Vsub2に変更する。

(もっと読む)

半導体記憶装置

【課題】抵抗変化メモリセルに充分な電流を流すことができる半導体記憶装置を提供する。

【解決手段】互いに交差するように形成されたワード線WLj及びビット線BLiと、これら配線の各交差部に配置され、ダイオードDIと可変抵抗素子VRとを直列接続してなるメモリセルMCを含むメモリセルアレイとを備える。ダイオードDIは、n+型層D3とp+型層D1とを有する。n+型層D3の少なくとも一部がシリコン−カーバイド混合物(Si1−xCx(0<x<1))で構成され、p+型層D1がシリコン(Si)で構成されている。

(もっと読む)

抵抗変化型メモリ

【課題】抵抗変化型メモリの動作特性を向上する。

【解決手段】本発明の一態様に関わる抵抗変化型メモリは、複数のブロックBKが設けられるメモリセルアレイと、複数のブロック内に設けられる複数の抵抗変化型記憶素子と、複数のブロック内に設けられ、抵抗変化型記憶素子に接続される第1及び第2の配線BL,WLと、前記複数のブロックにおいて動作の対象となる選択ブロック及び前記選択ブロックを除く複数の非選択ブロックの状態をそれぞれ制御する制御回路と、を具備し、

制御回路は、選択ブロックを動作させている期間中に、非選択ブロック内の第1及び第2の配線BL,WLに電位VUXを供給する。

(もっと読む)

半導体不揮発記憶装置

【課題】本発明は、複数電圧源を用意することなくFeFET単体へ多値記憶を行うことができる半導体不揮発記憶装置を提供することを課題とする。

【解決手段】強誘電体に、同一高さで、異なる幅のパルス電圧を印加して、異なる総分極量を与え、その総分極量の違いに応じた異なる記憶状態を作る多値強誘体メモリセルを有する半導体不揮発記憶装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新たなレイアウトパターンを作成せずにNMOSの駆動力を向上することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板100と、第1の導電型の第1の半導体素子が設けられる半導体基板100に形成される第1の半導体素子領域と、第2の導電型の第2の半導体素子が設けられる半導体基板100に形成される第2の半導体素子領域と、第1の半導体素子領域と第2の半導体素子領域とを分離する素子分離領域120とを備え、第1の半導体素子領域は、第1の半導体素子領域に隣接する素子分離領域120より高い位置に形成され、素子分離領域120の表面からの第1の半導体素子領域の表面までの距離が、第1の半導体素子領域の上面視における幅以下である。

(もっと読む)

複数メモリ層を有するメモリセルを含む記憶装置

【課題】各種干渉を排除し、寸法を縮小するため積層した複数メモリ層を有し、複数データ値を記憶するよう適合された非磁気メモリセルを用いた記憶装置を提供する。

【解決手段】記憶装置100は制御器102と制御器102を介してアクセス可能な複数個の抵抗性基本メモリセル106とを含む。複数個の抵抗性基本メモリセル106の各抵抗性基本メモリセルは、複数個のデータ値を記憶するヒステリシス特性を有するように選択された複数個のメモリ層130,132、134、136を含み、第1外部電極122と第2外部電極124との間に挟まれる。第1外部電極122は第1スイッチ108に結合され、第2外部電極124は第2スイッチ110に結合される。

(もっと読む)

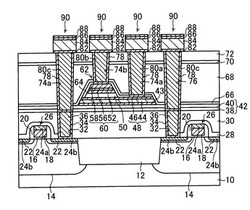

半導体装置及びその製造方法

【課題】ゾルゲル法又はスパッタ法により強誘電体膜等の容量絶縁膜を形成する場合であっても、その配向をより一層揃えることができる半導体装置及びその製造方法を提供する。

【解決手段】下部電極膜の一部であるアモルファス状のIr酸化膜54を形成した後、その上にPt膜91を形成する。Ir酸化膜54がどの方位にも配向していないため、Pt膜91は自己配向し、表面のミラー指数は(111)となる。次いで、Pt膜91上にPt膜92を形成する。Pt膜92はPt膜91の配向を引き継ぐため、Pt膜92の表面のミラー指数も(111)となる。その後、Pt膜92上に、スパッタ法により容量絶縁膜55を形成する。続いて、酸素を含む雰囲気中でRTAを行うことにより、容量絶縁膜55の全体を柱状晶にする。容量絶縁膜55を構成する柱状晶は、Pt膜92の配向を引き継ぐため、その表面のミラー指数も(111)となる。

(もっと読む)

圧電磁器および圧電素子

【課題】 圧動的d33定数が大きく、200℃の高温下においても使用可能であり、室温の動的d33定数に対する200℃の動的d33定数の変化の小さい圧電磁器および圧電素子を提供する。

【解決手段】 圧電磁器を組成式でBi4Ti3O12・β[(1−γM1TiO3・γM2M3O3]と表したとき、0.405≦β≦0.498、0≦γ≦0.3を満足するとともに、M1が、Sr、Ba、Ca、(Bi0.5Na0.5)、(Bi0.5Li0.5)および(Bi0.5K0.5)のうち少なくとも1種であり、M2が、Bi、Na、KおよびLiのうち少なくとも1種であり、M3が、FeおよびNbのうち少なくとも1種であるビスマス層状化合物の主成分100質量部に対して、MnおよびFeのうち少なくとも1種を酸化物(MnO2、Fe2O3)換算の合量で0.05〜1質量部含有することを特徴とする。

(もっと読む)

非晶質合金酸化層を含む不揮発性メモリ素子

【課題】非晶質合金酸化層を含む不揮発性メモリ素子を提供する。

【解決手段】不揮発性半導体メモリ素子において、下部電極と、下部電極上に非晶質合金酸化物を含んで形成された酸化層と、酸化層上に形成された上部電極とを備える非晶質合金酸化層を含む不揮発性メモリ素子である。

(もっと読む)

強誘電体薄膜

【課題】 Si単結晶基板上に強誘電体薄膜を形成するに際し、膜内の応力を制御して自発分極値の低下を防ぐことを目的とする。

【解決手段】 Si単結晶基板上に形成された強誘電体材料からなるエピタキシャル強誘電体薄膜であり、この強誘電体薄膜の結晶面のうち、前記Si単結晶基板表面の結晶面に平行な結晶面をZF面とし、ZF面間の距離をzFとし、強誘電体薄膜構成材料のバルク状態でのZF面間の距離をzF0としたとき、0.980≦zF/zF0≦1.010であり、前記強誘電体材料が、ペロブスカイト型結晶構造を有する、化学式ABO3(AはCa、Ba、Sr、K、Na、Li、LaおよびCdから選ばれた1種以上であり、BはTi、Zr、TaおよびNbから選ばれた1種以上である)で表される化合物又は希土類元素含有チタン酸鉛であり、厚さが2〜100nmである強誘電体薄膜。

(もっと読む)

1 - 12 / 12

[ Back to top ]