Fターム[5F101BA48]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | 絶縁膜材料 (2,488) | 不純物含有 (46)

Fターム[5F101BA48]に分類される特許

1 - 20 / 46

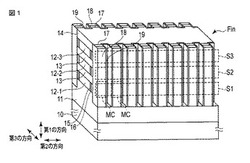

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

不揮発性半導体メモリ

【課題】 従来のMONOSは、SiNに電荷を蓄積する構成であるが、電荷蓄積量が不十分であり閾値電圧変化幅を大きく取れず、またHfO2,ZrO2,TiO2中へLa系元素を導入した技術ではドーパント導入による電荷の高密度化は実現が困難である。

【解決手段】 窒化シリコン膜よりも十分に誘電率の高いZr酸化物、Hf酸化物等の窒化シリコンよりも十分に高い誘電率を有する金属酸化物を母体材料として、その中に電子の出し入れが可能なトラップレベルを発生させるために、価数が2つ上(VI価)以上の高価数物質を適量添加する構成の電荷蓄積層を有する不揮発性半導体メモリである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持特性の良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体層SMLと、半導体層に対向して設けられた第1絶縁層I1と、半導体層と第1絶縁層との間に設けられた第2絶縁層I2と、第1絶縁層と第2絶縁層との間に設けられた機能層I3と、第1絶縁層の半導体層とは反対の側に設けられ、互いに離間した第1ゲート電極G1及び第2ゲート電極G2と、を備えた不揮発性半導体記憶装置が提供される。機能層のうちの第1ゲート電極に対向する第1領域R1、及び、機能層のうちの第2ゲート電極に対向する第2領域R2の電荷蓄積能は、機能層のうちの第1領域と第2領域との間の第3領域R3とは異なる。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明の目的は、書き込み/消去特性が向上しつつ、電荷保持特性、が向上した、MONOS型メモリを、簡単、且つ、再現性高く、形成する方法を提供することである。

【解決手段】本発明の半導体装置は、シリコン基板上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された電荷蓄積膜と、電荷蓄積膜上に形成されたブロック膜と、ブロック膜上に形成された制御ゲート電極膜と、を備えるMONOS型メモリセルであって、トンネル絶縁膜は、シリコン基板上に形成された第1のシリコン酸化膜と、第1のシリコン酸化膜上に形成されたボロンを含むシリコン窒化膜と、シリコン窒化膜上に形成された第2のシリコン酸化膜と、を備えたものである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御ゲート電極からリークした電子のエネルギーの増加を抑制し、トンネル絶縁膜の絶縁性の劣化を防止する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、半導体層101と、半導体層101の表面に形成された第1の絶縁膜102と、第1の絶縁膜102の表面に形成された電荷蓄積膜103と、電荷蓄積膜の表面に形成された第2の絶縁膜104と、第2の絶縁膜104の表面に形成された制御ゲート電極105とを具備し、電荷蓄積膜103及び第2の絶縁膜104の少なくとも一方に、散乱によって電子のエネルギーを減少させる非弾性散乱層が少なくとも一層含まれている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

半導体装置,及び半導体装置の製造方法

【課題】上部絶縁層と素子分離絶縁層の界面に起因する信頼性劣化が抑制された半導体装置を提供する。

【解決手段】半導体装置は,半導体基板と,前記半導体基板上に配置され,かつトンネル絶縁膜,電荷蓄積層,上部絶縁層,および制御電極が順に積層される積層構造と,前記積層構造の側面に配置される素子分離絶縁層と,前記半導体基板の前記トンネル絶縁膜の両側に形成された不純物ドーピング層と,を具え,前記素子分離絶縁層は,SiO2,SiN及びSiONの少なくとも一つからなり,前記上部絶縁層は,希土類金属,Y,Zr,及びHfからなる群より選ばれる少なくとも一つの金属M,及びSiを含む酸化物であり,前記電荷蓄積層,前記上部絶縁層,前記制御電極それぞれのチャネル長方向の長さLcharge,Ltop,Lgateが関係「Lcharge,Lgate < Ltop」を満たす。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高電界領域及び低電界領域のリーク電流を低減する揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101の表面領域に互いに離間して設けられたソース/ドレイン領域111と、ソース/ドレイン領域111間のチャネル上に設けられたトンネル絶縁膜102と、トンネル絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜105と、第1の誘電体膜105上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜106と、第2の誘電体膜106上に設けられた制御ゲート電極107とを含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリウィンドウが広い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置1において、半導体基板11上にトンネル絶縁膜12及びブロック絶縁膜13を設け、その上に制御ゲート電極18を設ける。そして、トンネル絶縁膜12とブロック絶縁膜13との間に、電荷蓄積粒15を分散させる。電荷蓄積粒15は、シリコン窒化物からなる窒化部16と、窒化部16に接し、シリコンからなるシリコン部17とにより構成する。電荷蓄積粒15は、シリコン窒化膜の表面上にシリコンを堆積させることにより、複数のシリコン粒子を形成した後、シリコン窒化膜をシリコン粒子毎に分断することによって形成されたものである。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

半導体記憶素子、半導体記憶素子の製造方法

【課題】従来のSiNを用いた電荷蓄積膜に比べ、高効率に電荷を蓄積および消去でき、かつ、蓄積した電荷を長時間保持する半導体記憶素子、半導体記憶素子の製造方法を得る。

【解決手段】この半導体記憶素子は、半導体基板に設けられたソース領域およびドレイン領域と、ソース領域およびドレイン領域との間の半導体基板上に設けられたトンネル絶縁膜と、トンネル絶縁膜上に設けられた電荷蓄積膜と、電荷蓄積膜上に設けられたブロック絶縁膜と、ブロック絶縁膜上に設けられたゲート電極と、電荷蓄積層とブロック絶縁膜との界面付近に設けられた気体分子を含む領域とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】下層の絶縁膜が窒化するのを抑制するとともに上層の絶縁膜からの酸素の拡散を抑制して電荷捕獲密度の低下を可及的に防止することを可能にする。

【解決手段】第1絶縁膜2と、第1絶縁膜上に形成され、窒素が添加されたアモルファスシリコン層4aと、アモルファスシリコン層上に形成された第1窒化シリコン層4bと、第1窒化シリコン層上に形成された第2絶縁膜10と、を備えていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】最適化されたトンネル絶縁膜を有する半導体装置を提供する。

【解決手段】半導体領域101と、半導体領域の表面に形成されたトンネル絶縁膜103と、トンネル絶縁膜の表面に形成され、シリコン及び窒素を含有する電荷蓄積絶縁膜104と、電荷蓄積絶縁膜の表面に形成されたブロック絶縁膜105と、ブロック絶縁膜の表面に形成された制御ゲート電極106と、を備え、トンネル絶縁膜は、半導体領域の表面に形成され、シリコン及び酸素を含有する第1の絶縁膜103aと、第1の絶縁膜の表面に形成された第2の絶縁膜103bと、第2の絶縁膜の表面に形成され、シリコン及び酸素を含有する第3の絶縁膜103cと、を有し、第2の絶縁膜中の電荷トラップ準位密度は、電荷蓄積絶縁膜中の電荷トラップ準位密度よりも低い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】微細化してもメモリセル間の干渉が少ない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板上にそれぞれ複数の絶縁膜15及び電極膜WLを交互に積層させてメモリ積層体を形成する。このとき、電極膜WLはシリコンにより形成し、その内部にシリコン窒化物からなる粒子23を分散させる。次に、このメモリ積層体に貫通ホール20bを形成する。次に、熱酸化処理を行い、電極膜WLにおける貫通ホール20bに面した部分を酸化し、ゲート絶縁膜22を形成する。このとき、ゲート絶縁膜22内に粒子23が取り込まれる。次に、貫通ホール20bの側面上にトンネル絶縁膜24を形成し、貫通ホール20bの内部にシリコンピラーSPを埋設する。このようにして製造された不揮発性半導体記憶装置1においては、粒子23がメモリセルの電荷蓄積部分となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル間の干渉を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】NAND型メモリ1において、半導体基板11の表面上に、トンネル絶縁層12、電荷蓄積層13、電荷ブロック層14を設け、その上に、チャネル長方向に沿ってそれぞれ複数の制御ゲート電極15及びセル間絶縁膜16を交互に設ける。そして、電荷ブロック層14におけるセル間絶縁膜16の直下域に相当する部分14bに塩素を導入し、部分14bの誘電率を電荷ブロック層14における制御ゲート電極15の直下域に相当する部分14aの誘電率よりも低くする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルにおけるゲート絶縁膜(トンネル絶縁膜)の改善によってデバイスの動作の信頼性を向上させること。

【解決手段】シリコン基板1とゲート電極4の間に、シリコン基板1側から順にシリコン酸化膜3f、シリコン窒化膜3d、シリコン酸化膜3bが積層した絶縁膜3が介在した半導体記憶装置であって、シリコン酸化膜3fとシリコン窒化膜3dの間の界面、シリコン窒化膜3dとシリコン酸化膜3bの間の界面、及びシリコン酸化膜3bとゲート電極4の間の界面の全ての界面に水素吸蔵膜3a、3c、3eが介在する。

(もっと読む)

1 - 20 / 46

[ Back to top ]