Fターム[5F101BB08]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | CG材料(多結晶以外のもの) (838)

Fターム[5F101BB08]に分類される特許

121 - 140 / 838

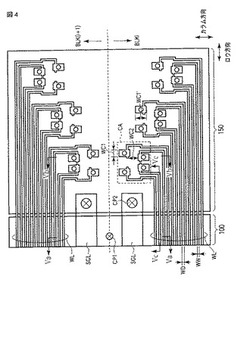

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置の製造方法

【課題】周辺回路素子の寿命を長くすると共に、後工程の熱処理等により周辺回路領域の素子分離溝部分に結晶欠陥が発生することを防止する。

【解決手段】本実施形態の半導体装置の製造方法は、半導体基板上の第1の領域に複数のメモリセルを形成し、前記半導体基板上の第2の領域に周辺回路素子を形成する半導体装置の製造方法であって、前記第1の領域に第1の開口幅を有する複数の第1の素子分離溝、前記第2の領域に前記第1の開口幅よりも広い第2の開口幅を有する第2の素子分離溝をそれぞれ形成する工程を備えた。さらに、前記第1の素子分離溝の内面に第1の膜厚の酸化膜を、前記第2の素子分離溝の内面に前記第1の膜厚よりも厚い第2の膜厚の酸化膜を、プラズマ酸化により一括形成する工程を備えた。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定のレイアウト面積内において複数の抵抗値が得られる抵抗素子を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板13上に配置された絶縁膜14と、絶縁膜14上に配置された導電層12と、導電層12上に配置された絶縁膜16と、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Aと、導電層11Aに接続されたコンタクト24Aと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Bと、導電層11Bに接続されたコンタクト24Bと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Cと、導電層11Cに接続されたコンタクト24Cとを備える。導電層12はフローティングゲート層と同じ材料から形成され、導電層11A、11B、11Cはコントロールゲート層と同じ材料から形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】記憶密度を高めた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、2積層体、第1、2半導体ピラー、及び分断絶縁層を備えた不揮発性半導体記憶装置が提供される。第1、2積層体は、第1軸に沿って積層された複数の第1、2電極膜と、第1、2電極膜の間の第1、2電極間絶縁膜と、を含み、第1軸に沿う第1、2貫通ホールが設けられる。第2積層体は、第1軸と直交する第2軸に沿って第1積層体と並ぶ。第1、2半導体ピラーは第1、2貫通ホールに埋め込まれる。分断絶縁層は第1、2電極膜を分断する。第1、2貫通ホールの分断絶縁層の側の側面は、第1、2軸に直交する第3軸を含み第1軸を含む平面と平行な部分を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元に積層されたメモリセルトランジスタにおける誤動作を防止する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20と、半導体基板の上方に形成された第1導電層40と、第1導電層の上方に順に積層された第2導電層43、電極間絶縁膜53’、および第3導電層43と、一対の貫通ホール49の内面上、および一対の貫通ホールの下端を連結させる連結ホール50の内面上に形成されたブロック絶縁膜53と、電荷蓄積層54と、トンネル絶縁膜55と、半導体層SPと、一対の貫通ホールの間に位置し、第2導電層、電極間絶縁膜、および第3導電層を分断するスリット46内に埋め込まれた絶縁材59と、第2導電層および第3導電層の表面上に形成されたシリサイド層58と、を具備し、スリットの内面に沿った第2導電層と第3導電層との間の距離は、積層方向に沿った第2導電層と第3導電層との距離よりも大きい。

(もっと読む)

不揮発性半導体記憶装置

【課題】高駆動力と高信頼性を実現する選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、選択ゲートスイッチトランジスタを備える不揮発性半導体記憶装置である。そして、この選択ゲートスイッチトランジスタが、半導体基板上に形成されるゲート絶縁膜と、ゲート絶縁膜上に形成されるゲート電極と、半導体基板中に、ゲート電極を挟むように設けられる第1のソース・ドレイン領域と第2のソース・ドレイン領域とを備えている。そして、第1のソース・ドレイン領域が、第1のn型不純物層と、第1のn型不純物層よりも不純物濃度が高く深さの浅い第2のn型不純物層を備えている。さらに、第2のソース・ドレイン領域が、第1のn型不純物層よりも不純物濃度が低く深さの浅い第3のn型不純物層と、第3のn型不純物層よりも不純物濃度が高く深さの深い第4のn型不純物層を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作特性の向上を図ることができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に間隔をあけて設けられた複数のメモリセルと、前記メモリセルの側壁に形成された絶縁膜と、を備えている。そして、前記絶縁膜は、前記メモリセル同士の間に形成された空隙部の上方において、隣接する前記メモリセルに向けて突出する突出部を有している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】トランジスタの素子領域の端部に形成される寄生トランジスタの影響を軽減することができる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板10内に形成された素子領域10Aと、素子領域10A上に形成された第1のゲート絶縁膜14と、第1のゲート絶縁膜14上に形成された第1のゲート電極15と、第1のゲート電極15上に形成され、開口を有するゲート間絶縁膜16と、ゲート間絶縁膜16上に形成され、開口を介して第1のゲート電極15と接する第2のゲート電極12と、素子領域10A、第1のゲート絶縁膜14および第1のゲート電極15によって形成された積層構造を囲む素子分離領域11とを備える。素子領域10Aの側面、第1のゲート絶縁膜14の側面及び第1のゲート電極15の側面と、素子分離領域11との間には空隙18Aが形成されている。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】1つの実施形態は、例えば、トンネル電流を容易に増加できる半導体記憶装置の製造方法、及び半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、半導体記憶装置の製造方法が提供される。半導体記憶装置の製造方法では、Ge、Sn、C、及びNのいずれかの不純物を半導体基板の表面に導入する。半導体記憶装置の製造方法では、前記不純物が導入された前記半導体基板の表面にトンネル絶縁膜が形成されるように、前記半導体基板を熱酸化する。半導体記憶装置の製造方法では、前記トンネル絶縁膜上に電荷蓄積層を有するゲートを形成する。半導体記憶装置の製造方法では、前記ゲートと自己整合的に前記半導体基板内に不純物拡散領域を形成する。

(もっと読む)

121 - 140 / 838

[ Back to top ]