Fターム[5F101BE17]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 保護 (34)

Fターム[5F101BE17]に分類される特許

21 - 34 / 34

半導体記憶装置及びその製造方法

【課題】ワード線形成用の導電層を堆積した後の工程においても、ワード線の帯電による高電圧の印加からメモリセルを保護することができるようにする。

【解決手段】半導体記憶装置は、P型ウェル1に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域Aと、複数のメモリセルのうち同一の行に並ぶメモリセル同士を共通に接続する複数のワード線13と、P型ウェル1にメモリセルアレイ領域Aと分離して形成された保護ダイオード領域Bとを有している。保護ダイオード領域Bには、P型ウェル1の上部に形成されたN型拡散層9とP型ウェル1とが接合してなる保護ダイオード素子が構成され、各ワード線13は、保護ダイオード領域Bに延伸してN型拡散層9と直接に接続されることにより、保護ダイオード素子と電気的に接続されている。

(もっと読む)

半導体装置およびその駆動方法

【課題】フラッシュメモリセルの消去特性の安定化を図ると共に書き込み動作から消去動作に切り替える際の消費電力の増大を抑制し、かつ切り替え動作を高速化する。

【解決手段】半導体素子Aと半導体素子の帯電を防止する保護素子Bとを備える。半導体素子は第1の入力線Vin1と接続されており、半導体素子と第1の入力線との間に位置する第1のノードN1と接地電位との間に保護素子が接続されている。保護素子は、第1のノードと接地電位との間に、第1のノード側から順に互いに逆向きに直列接続された第1のPN接合ダイオードD1および第2のPN接合ダイオードD2と、第1のPN接合ダイオードと第2のPN接合ダイオードとの接続点である第2のノードN2にドレインが接続され、接地電位にソースが接続され、第2の入力線Vin2にゲートが接続されたMIS型トランジスタT1とからなる。

(もっと読む)

半導体装置

【課題】MONOS型メモリセル構造形成以降の製造工程中に被った過剰帯電による誤書込みを防止する。

【解決手段】第1導電型領域1上に素子分離領域14で分離形成された保護素子領域13およびメモリセル領域12と、メモリセル領域上に形成されたMONOS型メモリセルと、保護素子領域上に形成されたMOS型トランジスタと、保護素子領域に形成された第1導電型拡散層5とを備える。ここで、MOS型トランジスタのゲート電極2はMONOS型メモリセルのゲート電極2が素子分離領域を越えて延在するように形成され、第1導電型拡散層はMOS型トランジスタに含まれる第2導電型拡散層4と導電材料15によって電気的に短絡され、MOS型トランジスタのゲート絶縁膜3の耐圧はMONOS型メモリセルのゲート絶縁膜の耐圧よりも低い。

(もっと読む)

半導体集積回路装置の製造方法

【課題】

不揮発性メモリと多結晶シリコン薄膜抵抗素子の高精度化、高機能化とを安価に実現できる半導体装置の製造方法の提供を目的とする。

【解決手段】

不揮発性メモリのコントロールゲート電極と配線、多結晶シリコン薄膜抵抗素子を比較的薄い多結晶シリコン膜で形成し、ESD保護素子形成のための高濃度不純物注入をコントロールゲート配線にも行うことを特徴とする製造方法。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 製造工程中のプラズマ工程において、素子分離領域に入射した電磁波が不揮発性半導体記憶装置の特性を劣化させるのを防止する。

【解決手段】 半導体基板1上に保護酸化シリコン膜2および窒化シリコン膜3を形成する。つぎに、保護酸化シリコン膜2および窒化シリコン膜2の所定領域を開口する。つぎに、所定領域が開口された保護酸化シリコン膜2および窒化シリコン膜3をマスクとして半導体基板1をエッチングすることにより半導体基板1に素子分離用の溝を形成し、溝の側壁面および底面に沿うように電磁波を吸収する絶縁性の遮光膜402を形成する。つぎに、半導体基板1の溝以外の部分の上方に形成された、遮光膜402を除去して、窒化シリコン膜3を露出させる。つぎに、半導体基板1の溝以外の部分の上方の窒化シリコン膜3および保護酸化シリコン膜2を除去して、半導体基板1の溝以外の部分を露出させる。

(もっと読む)

IC部品を保護するためのシステムおよび方法

1つの実施の形態は、集積回路(IC)(100)の少なくとも1つの部品を保護するためのシステムを提供する。システムは、ICの端子と少なくとも1つの部品(108)との間に電気的に接続された切断要素(104)を含む。切断要素は、端子から少なくとも1つの部品に電気信号が伝搬するのを許容する第1の状態と、端子を少なくとも1つの部品から電気的に切断する高インピーダンス状態に対応する第2の状態とを有するように構成される。制御システム(110)は、少なくとも1つの予め決められた起動条件に基づいて、切断要素を第1の状態から第2の状態に遷移させるように構成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 拡散ビット線とこれに交差するワード線を備えたトランジスタアレイにおいて、アレイ面積の増大を抑制しつつ、ゲート保護機能を備えた半導体装置を実現する。

【解決手段】 トランジスタは、ゲート電極2、ゲート絶縁膜4および拡散ビット線5を構成する拡散層とからなる。拡散ビット線5上にはビット線絶縁膜3が形成されている。ゲート絶縁膜と同一の絶縁膜を介して、ビット線絶縁膜と平行に拡散ビット線方向に配置されたゲート保護用絶縁膜6を有する。トランジスタのゲート電極は、ゲート絶縁膜上、ビット線絶縁膜上、ゲート絶縁膜と同一の絶縁膜上およびゲート保護用絶縁膜上に跨るように延伸して配置されることによってワード線を構成するとともに、ゲート電極、ゲート保護用絶縁膜および基板とによって構成されるMOS型ダイオードと接続されている。ここで、ゲート保護用絶縁膜の耐圧は、ゲート絶縁膜の耐圧よりも低い。

(もっと読む)

半導体記憶装置

【課題】 微細化され、かつ、電荷保持特性の良好な不揮発性メモリを有する半導体装置を提供する。

【解決手段】不揮発性メモリ20は、前記半導体層10に設けられた埋込絶縁層12により画定された第1領域10Xおよび第2領域10Y、Zと、前記第1領域10Xに設けられ、不純物層28からなるコントロールゲートと、前記第1領域10Xおよび前記第2領域10Y、Zの上方に設けられたゲート絶縁層22と、前記ゲート絶縁層22の上方に設けられ、前記第1領域10Xおよび前記第2領域10Y、Zの上方で連続した一の層からなるフローティングゲート電極24と、前記第2領域10Y、Zにおいて、前記フローティングゲート電極24の側方の前記半導体層10に設けられ、ソース領域またはドレイン領域となる不純物領域32、34とからなる。また、前記複数の不揮発性メモリ20の前記コントロールゲート28は、連続した不純物層からなる。

(もっと読む)

半導体装置

【課題】横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】第1半導体素子120を含み、その周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、 第2半導体素子120´を含み、その周囲に設けられた第2遮光壁50´により画定され、前記第1被遮光領域10Aと隣り合う位置に設けられた第2被遮光領域10A´と、 前記第1遮光壁50に設けられた第1開孔52と、 前記第2遮光壁50´に設けられ前記第1開孔52と対向して位置する第2開孔52´と、 前記第1半導体素子120と接続され、前記第1開孔52から前記第1被遮光領域10Aの外側に引き出された第1配線層24と、 前記第2半導体素子120´と接続され、前記第2開孔52´から前記第2被遮光領域10A´の外側に引き出された第2配線層24´と、を含む半導体装置。

(もっと読む)

半導体装置およびその駆動方法

【課題】 MOS型ダイオード素子等を用いた工程中チャージアップ保護素子のゲート絶縁膜の定電圧TDDB寿命を確保する。

【解決手段】 N型半導体基板1上に、N型ウェル2で互いに電気的に分離された、第1のP型ウェル3と第2のP型ウェル4および素子分離膜5が形成されている。第1のP型ウェル3上に、第1のゲート絶縁膜6とゲート電極8からなるMOS型トランジスタが形成され、第2のP型ウェル4上に、第2のゲート絶縁膜7とゲート電極8からなるMOS型ダイオード素子が形成されている。第2のP型ウェル4に印加する第1の電圧を、第1のゲート電極8に印加する第2の電圧と第1のP型ウェル3に印加する第3の電圧との間の電圧に設定する回路を備えている。

(もっと読む)

半導体装置

【課題】 MOS型トランジスタ素子のソース・ドレイン拡散層上のゲート絶縁膜を保護することで、MOS型トランジスタ素子の工程中チャージアップ保護性能の向上を図る。

【解決手段】 P型ウェル2内のソース・ドレイン拡散層間に形成された、第1のゲート絶縁膜5およびゲート電極7を有するMOS型トランジスタ素子と、P型ウェル2内に形成された、第2のゲート絶縁膜6およびゲート電極7を有する第1のMOS型ダイオード素子と、N型ウェル3内に形成された、第2のゲート絶縁膜6およびゲート電極7を有する第2のMOS型半導体素子とからなり、第2のゲート絶縁膜6の耐圧は第1のゲート絶縁膜5の耐圧よりも低く設定され、それぞれのゲート電極7は互いに電気的に接続されている。

(もっと読む)

保護回路

【課題】 通常動作に影響を与えることなく、サージ耐圧及びサージ電流耐量を飛躍的に向上可能な保護回路を提供する。

【解決手段】 入出力端子2に印加された正及び負の過電圧を検知する検知回路11aと、正及び負の過電圧が検知された場合に入出力端子2及び内部回路3間を非導通状態として正及び負の過電圧を遮断する遮断回路12aとを備える。

(もっと読む)

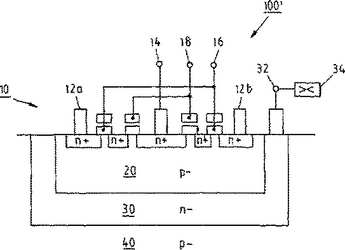

光照射から保護される電子メモリ構成要素

いわゆる光照射の形態をとる光入射が直接検出されるか、または不感時間なしに直ちに感知される(=チップ発展への寄与)ように、少なくとも1つのドープ受容基板(20)中に埋め込まれおよび/または填め込まれる少なくとも1つのメモリ・セル・マトリックス(10)を備える、電子メモリ構成要素(100または100’)を発展させるために、受容基板(20)は、メモリ・セル・マトリックス(10)から離れたその表面の少なくとも1つが、少なくとも部分的におよび/または受容基板(20)とは反対のドープ型の少なくとも1つの上部/保護基板(30)によって覆われおよび/または囲まれること、および基板(20または30)の少なくとも1つ、たとえば受容基板(20)および/または特に上部/保護基板(30)が、光入射時に生成される電荷キャリアによって生じる電圧または電流の検出のために少なくとも1つの回路構成(それぞれ24または34)に接触(12aまたは12b)または接続(32)することが提案される。  (もっと読む)

(もっと読む)

フラッシュメモリ装置のワード線を保護するための方法および装置

製造中に、プロセスに関連する帯電からフラッシュメモリのワード線(WL)およびメモリセル(101)を保護するための方法と構造とが与えられる。ドープされたポリシリコンのワード線(110a)の端部にドープされていないポリシリコン(110b)が形成され、抵抗(110b)が生成される。これを通じて、プロセスにより生じる電荷が、基板(102)に結合された、ドープされたポリシリコン放電構造(110c)へ放電される。ワード線抵抗(110b)、および、放電構造(110c)は、単一のパターニングされたポリシリコン構造として形成される。ワード線(110a)および放電部分(110c)は導電性になるように選択的にドープされ、また、抵抗部分(110b)は、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。  (もっと読む)

(もっと読む)

21 - 34 / 34

[ Back to top ]