Fターム[5F102GA11]の内容

接合型電界効果トランジスタ (42,929) | 集積化 (1,005) | FETと他の素子・部品 (577)

Fターム[5F102GA11]の下位に属するFターム

バイポーラ、トランジスタ (59)

ダイオード (194)

L(インダクタンス) (29)

C(キャパシタ) (106)

R(抵抗) (151)

ストリップ線路 (25)

発光・受光素子 (5)

Fターム[5F102GA11]に分類される特許

1 - 8 / 8

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体装置

【課題】素子温度の上昇を抑制する半導体装置を提供する。

【解決手段】動作周波数fで動作可能な半導体装置であって、熱拡散率Dの基板と、基板上に形成され、ワイドギャップ半導体素子で横型素子の第1のトランジスタで構成される第1の素子ユニット12と、基板上に第1の素子ユニット12に隣接して形成され、第1のトランジスタと異なるタイミングで動作するワイドギャップ半導体素子で横型素子の第2のトランジスタで構成される第2の素子ユニット14とを備え、第1の素子ユニット12の重心と、第2の素子ユニット14の重心との距離が熱拡散長(D/πf)1/2の2倍以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】

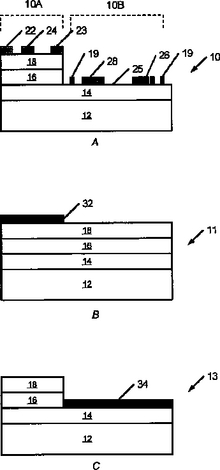

【解決手段】本発明は基板と、該基板上のGaNを含む第1層とAlGaNを含む第2層とを含む構成を含む半導体装置に関する。第1層上に第2層を堆積させ、第1層及び第2層は少なくとも部分的に基板を被覆する。また該構造はダイヤモンドを含む第3層を含む。

(もっと読む)

磁気センサ、ホール素子、ホールIC、磁気抵抗効果素子、ホール素子の作製方法、および磁気抵抗効果素子の作製方法

【課題】300℃以上の高温域において従来のものよりも良好に動作する磁気センサを提供する。

【解決手段】GaNからなり室温での電子濃度が1×1016/cm3以下である第1層2aと、AlxGa1-xN(0<x≦0.3)からなる第2層2bとを積層することで、ヘテロ接合界面を有する動作層2を形成する。これにより、二次元電子ガス領域2gにおけるキャリア移動度はより高められるとともに、キャリア濃度がより低減される。その結果、室温においては定電流駆動および定電圧駆動の双方で高い測定感度を有するとともに、高温でも定電流駆動によって室温と同程度の測定感度で使用できるホール素子が実現される。

(もっと読む)

半導体装置の製造方法

【課題】各素子の接続部分に発生する寄生容量等の問題を解消し、高い周波数の高周波信号についても、これを高精度に検波可能な装置を製造可能な技術を提供すること。

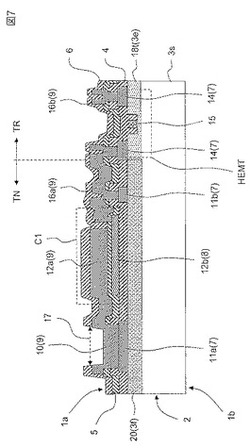

【解決手段】平面アンテナ3及び増幅回路5並びに検波回路7を一体形成するため、支持基板上に、増幅回路形成用の半導体層を積層し、この上層に、InP層15を形成し、更に、上層に、検波回路形成用の半導体層を積層して、基本部材を形成する。この後、基本部材の半導体層を加工して、検波回路7を形成し、この後に、検波回路7側の基本部材表面に、第二の支持基板40を貼り付ける。また、この後、基本部材形成時に最下層に配置した支持基板を取り除き、基本部材の上下を反転させて、基本部材に形成された増幅回路形成用の半導体層を加工し、増幅回路5及び平面アンテナ3を形成する。また、加工時には、増幅回路5と検波回路7とを、キャパシタ60により電気的に接続する。

(もっと読む)

化合物半導体装置

【課題】近接する2つの素子間に高濃度不純物領域を配置し、フローティング電位またはGND電位を印加することにより2つの素子間のアイソレーションを向上させる手法は、漏れた高周波信号のパワーが大きい場合に高濃度不純物領域の電位が変動してしまう。このため、結果として2つの素子間のアイソレーションが十分確保できなくなる問題があった。

【解決手段】近接する2つの素子間に伝導領域または金属層による分離素子を配置する。分離素子は高抵抗素子を接続し、直流端子パッドに接続する。また直流端子パッドから分離素子に至る接続経路は電位が高周波振動しない経路とする。これにより、少なくとも一方に高周波信号が伝搬する2つの素子の間に高周波GND電位を配置したこととなり、2つの素子間の高周波信号の漏れを防止できる。

(もっと読む)

窒化物ベースの集積音波デバイスおよび窒化物ベースの集積音波デバイスを製造する方法

モノリシック電子デバイスは、基板と、基板上に形成された半絶縁圧電III族窒化物エピタキシャル層と、エピタキシャル層上に表面弾性波デバイスを形成する一対の入力および出力インターディジタル変換器と、基板上に形成された少なくとも1つの電子デバイス(HEMT、MESFET、JFET、MOSFET、フォトダイオード、LEDなど)とを含む。電子デバイスをSAWデバイスから、反対にSAWデバイスを電子デバイスから電気的かつ音響的に分離するための分離手段が開示される。いくつかの実施形態ではSAWデバイスと電子デバイスとの間にトレンチが形成される。さらに、その上にSAWデバイスを製造することができる半絶縁III族窒化物エピタキシャル層を形成するためのイオン注入が開示される。インターディジタル変換器に隣接した吸収および/または反射部品が、SAWデバイスの動作を妨害する可能性がある不要な反射を低減させる。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]