Fターム[5F102GA17]の内容

接合型電界効果トランジスタ (42,929) | 集積化 (1,005) | FETと他の素子・部品 (577) | R(抵抗) (151)

Fターム[5F102GA17]に分類される特許

1 - 20 / 151

高周波回路装置

【課題】 電気的特性を向上させた高周波回路装置を提供する。

【解決手段】 高周波回路装置は、一端同士1331,1341が互いに離間して対向した2つの伝送線路133,134と、2つの伝送線路の一方の一端に実装され、該実装面となる下面電極30と、該実装時に下面電極の上方に位置する上面電極32を備えるキャパシタCと、2つの伝送線路の対向する一端同士の間の領域に配置され、一端同士を電気的に接続する抵抗素子Rと、キャパシタの上面電極と2つの伝送線路の他方との間を電気的に接続する接続導体135とを備える。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

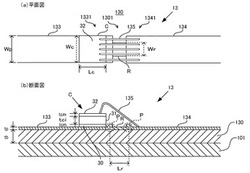

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因するクラック等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成されたGaN系化合物半導体積層構造3と、基板1とGaN系化合物半導体積層構造3との間に設けられたAlN系の応力緩和層2と、が設けられている。応力緩和層2のGaN系化合物半導体積層構造3と接する面に、深さが5nm以上の窪み2aが2×1010cm-2以上の個数密度で形成されている。

(もっと読む)

スイッチ装置

【課題】スイッチ素子のオン抵抗をより一層小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ素子10は、半導体基板104に絶縁膜15を介して接合された電界印加電極14を有している。駆動回路20の電界制御部22は、スイッチ素子10の電界印加電極14およびソース電極13に接続されており、電界印加電極14−ソース電極13間にバイアス電圧Veを印加する。電界制御部22は、閾値を超えるバイアス電圧Veをスイッチ素子10に印加することによって、電界印加電極14から半導体基板104のヘテロ接合界面に電界を印加する。要するに、スイッチ素子10がオン状態で、電界印加電極14から半導体基板104に印加される電界は、電界効果によってチャネル領域の電子濃度を高くし、スイッチ素子10のオン抵抗を小さくするように作用する。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電極のドレイン端の電界を緩和し、ゲート絶縁膜の破損を低減する。

【解決手段】窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップエネルギーが大きい窒化物半導体で形成された電子供給層112と、チャネル層108の上方に形成されたソース電極116およびドレイン電極118と、チャネル層108の上方に形成されたゲート電極120と、チャネル層108の上方に形成され、チャネル層108からホールを引き抜くホール引抜部126と、ゲート電極120およびホール引抜部126を、電気的に接続する接続部124と、を備える電界効果型トランジスタ100。

(もっと読む)

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に、第1の主電極Dswと第2の主電極Sswの間に配置された制御電極Gswを有するスイッチング素子Tswと、スイッチング素子Tswの第1の主電極Dswにアノード端子が接続された第1の整流素子D1、第1の整流素子D1のカソード端子に第1の主電極DD1が接続され、スイッチング素子Tswの制御電極Gswに第2の主電極SD1が接続された第1の駆動素子TD1、スイッチング素子Tswの制御電極Gswに第1の主電極DD2が接続され、スイッチング素子の第2の主電極Sswに第2の主電極SD2が接続された第2の駆動素子TD2、及び、第1の駆動素子TD1の制御電極GD1と第2の駆動素子TD2の制御電極GD2にそれぞれ入力される制御信号を受信する入力端子IN_H,IN_Lを有する駆動回路10とを備える。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

パッシブ発振防止用のIII族窒化物トランジスタ

【課題】パッシブ発振制御を有する半導体素子を提供する。

【解決手段】ソース電極202、ゲート電極208およびドレイン電極204を有するIII族窒化物トランジスタ200を含む。ダンピング抵抗器270がパッシブ発振制御をIII族窒化物トランジスタ200に提供するように構成される。ダンピング抵抗器270が少なくとも一つの集中抵抗器R1を含む。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

電界効果トランジスタ、半導体スイッチ回路、および通信機器

【課題】半導体スイッチのチップサイズを大きくすることなく、高調波特性を改善する。

【解決手段】FET1において、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられる複数のソース電極6を有するソース配線3と、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられて複数のソース電極6に対して並列方向に交互に配置される複数のドレイン電極7を有するドレイン配線4と、化合物半導体基板上に形成され、少なくとも前記並列方向に互いに隣り合うソース電極6とドレイン電極7との電極間に位置する部分を有するゲート配線5と、ゲート配線5が形成される領域にてゲート配線5下に形成され、複数のソース電極6と複数のドレイン電極7との各電極間に独立して設けられる複数の埋め込みゲート層8とを備えた。

(もっと読む)

半導体製造装置の洗浄装置及びそれを用いた半導体装置の製造方法

【課題】部品の洗浄効率を向上することができる半導体製造装置の洗浄装置及びそれを用いた半導体装置の製造方法を提供する。

【解決手段】半導体製造装置の洗浄装置1には、半導体製造装置の部品に付着した付着物の表面の酸化物を除去する酸化物除去部3と、酸化物除去部3により表面の酸化物が除去された付着物を除去する付着物除去部2と、が設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層のクラックをより一層低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基材1と、基材1の上方に形成された初期層2と、初期層2上に形成され、III−V族化合物半導体を含むコア層3と、が設けられている。初期層3として、コア層3に含まれるIII-V族化合物半導体のIII族原子の層が形成されている。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

1 - 20 / 151

[ Back to top ]