Fターム[5F102GN06]の内容

接合型電界効果トランジスタ (42,929) | 表面半導体層(ゲートメタル電極底面より高い位置にある層) (914) | 単一半導体層 (704) | 3−5族 (686) | GaAlAs (24)

Fターム[5F102GN06]に分類される特許

1 - 20 / 24

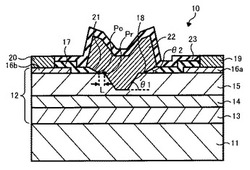

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】高周波モジュール中におけるスイッチング素子として用いられるHEMT素子を小型化する。

【解決手段】GaAsからなる基板1の主面上の素子分離部9で規定された活性領域内において、ゲート電極17は、1本で形成し、ソース電極13とドレイン電極14との間では紙面上下方向に延在し、それ以外の部分では左右方向に延在するようにパターニングすることにより、活性領域外に配置されるゲート電極17の割合を減じ、ゲートパッド17Aの面積を減じる。

(もっと読む)

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

半導体装置

【課題】オン抵抗の増加を抑制すると共にリーク電流を低減させることができる半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、ノンドープInGaAs層8と、ノンドープInGaAs層8上に形成された、第1リセス部を備えるSiドープGaAs層1と、ノンドープInGaAs層8とSiドープGaAs層1との間に形成され、第1リセス部内に設けられた第2リセス部を備える、ノンドープオーダ系InGaP層4とその上に形成されるノンドープGaAs層3からなる2層構造半導体層と、第2リセス部内において、ノンドープInGaAs層8上に設けられたCドープGaAs層13と、CドープGaAs層13と、ノンドープGaAs層3及びノンドープオーダ系InGaP層4の界面との間に設けられると共に、ノンドープオーダ系InGaP層4とCドープGaAs層13との間の一部には設けられていない側壁絶縁膜17とを備える。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】5族原料の使用量を低減しつつ、3−5族化合物半導体のp型キャリア濃度を制御する。

【解決手段】ベース基板を反応容器の内部に設置する段階と、反応容器に、3族元素の有機金属化合物からなる3族原料ガス、5族元素からなる5族原料ガス、および、半導体内にドープされてドナーとなる不純物を含む不純物ガスを供給して、ベース基板にp型3−5族化合物半導体をエピタキシャル成長させる段階とを備え、ベース基板にp型3−5族化合物半導体をエピタキシャル成長させる段階において、不純物ガスの流量、および3族原料ガスに対する5族原料ガスの流量比を、p型3−5族化合物半導体の残留キャリア濃度N(cm−3)および厚さd(cm)の積N×d(cm−2)が8.0×1011以下になるよう設定する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は半導体装置および半導体装置の製造方法に関し、半導体装置の洗浄工程において半導体装置の半導体層の腐食防止を可能とすることを目的とする。

【解決手段】本発明に係る半導体装置は、半導体層と、前記半導体層に接続した電極部と、前記電極部に接続した、前記半導体層および前記電極部の構成材料よりイオン化傾向の大きい金属からなる犠牲金属層と、を備える。本発明に係る半導体装置の製造方法は、半導体ウェハに、半導体層と前記半導体層に接続した電極部を有する半導体装置と、前記半導体層と電気的に接続した電気接触領域と、を形成する形成工程と、洗浄液の電位に対して負の電位を導き得る導電体を、前記電気接触領域に接続する接続工程と、前記半導体ウェハを前記洗浄液に浸漬した状態で、前記電気接触領域に前記負の電位を印加しながら、洗浄する洗浄工程と、を備える。

(もっと読む)

スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール

【課題】挿入損失を増大させることなくマルチゲートのゲート間の電位安定化が可能なスイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュールを提供すること。

【解決手段】電界効果型トランジスタを成すように、半導体基板上に形成された2個のオーミック電極39,40と、上記2個のオーミック電極の間に配置された少なくとも2個のゲート電極41,42と、隣り合うゲート電極の間に挟まれて配置された導電領域45とが備えられる。導電領域は、一端に、上記隣り合うゲート電極に挟まれている導電領域よりも幅が広い幅広部分を有し、隣り合うゲート電極の間の距離が幅広部分の幅よりも狭い。更に、幅広部分を介して2個のオーミック電極の間に直列に抵抗44,46が接続されている。

(もっと読む)

電界効果トランジスタ、半導体チップ及び半導体装置

【課題】均一性や生産性が高いと共に、高周波性能として、雑音指数が小さく、かつ付随利得の大きい電界効果トランジスタ(FET)、このFETを備える半導体チップ及び半導体装置を提供すること。

【解決手段】本発明のFET1は、GaAs半導体基板2の上に、i形GaAsバッファ層3と、i形InGaAs二次元電子ガス層4と、n形AlGaAs電子供給層5と、が積み上げられ、n形AlGaAs電子供給層5の上に線状にショットキー性接触するゲート電極12があり、ゲート電極12の両横から離れ、かつn形AlGaAs電子供給層5の上に、n形InGaPエッチング停止層6と、続いて同程度の横位置でn形GaAsコンタクト層7とが積み上げられ、n形GaAsコンタクト層7の上にコンタクト層7の端から離れて帯状にオーム性接触をする電極として各側にソース電極9とドレイン電極10とを備える。

(もっと読む)

スイッチ素子および電子機器

【課題】IMDや高調波歪の少ないスイッチ素子を提供する。

【解決手段】シャント回路に直列挿入されたシャントFET1Aと、シリーズ回路に直列挿入されたシリーズFET1Bとを備える。シャントFET1Aは、コンタクト層17内のゲート領域34上にゲート電極30を有し、コンタクト層17上のゲート電極30の両側にソース電極31およびドレイン電極32を有し、ゲート領域34の両側に一対のリセス35を有する。シリーズFET1Bは、コンタクト層17内のリセス40の底部に形成されたゲート領域45上にゲート電極41を有し、コンタクト層17上のリセス40の両側にソース電極42およびドレイン電極43を有する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】位置合わせの精度に依存しないでゲート電極とトレンチとの間の距離をゼロにすることができ、さらにステッパーの開口能力に依存しないでトレンチの開口幅を狭くすることの可能な電界効果トランジスタの製造方法を提供する。

【解決手段】拡散層17上に絶縁膜18Aと、開口径L1の開口部H1を有するレジスト層R1とを形成したのち(S1,S2)レジスト層R1をマスクとして絶縁膜18Aに開口部を形成する(S3)。レジスト層R1を除去したのち絶縁膜18Aをマスクとして拡散層17の露出部分にゲート領域20Aを形成する(S4)。開口径L2の開口部H2を有するレジスト層R2を形成したのち(S5)リフトオフにより開口部H2の部位にゲート電極21を形成する(S6)。ゲート電極21および絶縁膜18Aをマスクとしてゲート電極21の両脇に一対のトレンチ19を形成する(S7)。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】従来のFETにおいては、AlGaAs電子供給層とInGaPエッチングストップ層との界面にAlGaAsP層等の変成層が形成され、それによりショットキー特性の劣化が生じる。

【解決手段】FET1は、AlGaAsからなる電子供給層14と、電子供給層14上に設けられた、Alを含まない界面安定化層15と、界面安定化層15上に設けられた、InGaPからなるエッチングストップ層16と、エッチングストップ層16上に設けられた、GaAsからなるコンタクト層17と、を備えている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】従来のJ−FETにおいては、ゲート電流の通電前後で、しきい値電圧(VT)のシフトが発生するといった問題があった。

【解決手段】本発明の一実施形態に係るJ−FETは、第1導電型のキャリアを蓄積するアンドープInGaAsチャネル層5と、アンドープInGaAsチャネル層5上に設けられ、第2導電型の不純物を含有するp+型GaAs層17(半導体層)と、p+型GaAs層17上に設けられたゲート電極18と、を備えている。ここで、p+型GaAs層17中に含まれる水素濃度は、p+型GaAs層17の第2導電型のキャリア濃度よりも低い。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】受信側FFTと送信側FETを固定して用いるスイッチMMICでは、それぞれのFETのピンチオフ電圧を異ならせ、送信側および受信側のスイッチング素子として適切な特性に設計すればよい。しかし、HEMTにおいてリセスエッチングの深さ制御が困難であり、ピンチオフ電圧の再現性が悪い問題があった。

【解決手段】エッチングストップ用のInGaP層を2層有する基板を使用する。InGaP層とAlGaAs層の選択エッチングを使用することにより、再現性良く2種類のピンチオフ電圧を実現できる。また2種類のHEMTのゲート電極に埋め込みゲート電極構造を採用するが、PtがInGaP層に拡散しないようにコントロールすることで、耐圧を大幅に向上できる。

(もっと読む)

スイッチ集積回路装置およびその製造方法

【課題】高周波スイッチMMICにおいてD型HEMTとE型HEMTを同一基板に形成し、D型HEMTのゲート電極をInGaP層にPtを埋め込んだ埋め込みゲート構造とする場合、埋め込まれたPtがInGaP層表面において横方向に異常拡散するため耐圧が低くなるという問題があった。

【解決手段】AlGaAs層とInGaP層を繰り返し積層した第1〜第3ノンドープ層と安定層を有するエピタキシャル構造とし、D型HEMTの第2ゲート電極を第3ノンドープ層(AlGaAs層)上に設け、E型HEMTの第1ゲート電極を第1ノンドープ層上に設ける。第2ゲート電極をPt埋め込みゲート構造とし、埋め込まれたPtの底部を第3ノンドープ層中に留まらせ、InGaP層(第2ノンドープ層)にPtが達しないようにする。これによりInGaP層表面におけるPtの横方向異常拡散を防止し、大幅に耐圧を向上させることができる。

(もっと読む)

化合物半導体スイッチ回路装置およびその製造方法

【課題】スイッチMMICにおいて、ゲート配線と、ソース配線電極またはドレイン配線電極との交差部では容量が大きく、高周波信号の漏れが発生し、歪特性が悪い問題があった。

【解決手段】ゲート配線上を、比誘電率の大きい窒化膜(膜厚3000Å)と、比誘電率の小さい中空部(厚さ2μm)で被覆し、その上にソース配線電極またはドレイン配線電極を設ける。これにより交差部での容量を低減できる。またゲート電極の一端を延在して曲折部を形成し、曲折部をソース電極−ドレイン電極間に配置する。これによりスイッチMMICの全てのソース電極−ドレイン電極間に、ゲート電極(曲折部)またはゲート配線を配置できる。オフ側FETのゲート電極は高周波信号としてGND電位であるので、ドレイン電極−ソース電極間の高周波信号の漏れを防止でき、交差部の中空部の配置と併せてスイッチMMICの歪特性を大幅に向上できる。

(もっと読む)

化合物半導体スイッチ回路装置およびその製造方法

【課題】スイッチMMICにおいて、ゲート配線と、ソース配線電極またはドレイン配線電極との交差部では容量が大きく、高周波信号の漏れが発生し、歪特性が悪い問題があった。

【解決手段】ゲート配線上を、比誘電率の大きい窒化膜(膜厚3000Å)と、比誘電率の小さいポリイミド(膜厚2μm)で被覆し、その上にソース配線電極またはドレイン配線電極を設ける。これにより交差部での容量を低減できる。またゲート電極の一端を延在して曲折部を形成し、曲折部をソース電極−ドレイン電極間に配置する。これによりスイッチMMICの全てのソース電極−ドレイン電極間に、ゲート電極(曲折部)またはゲート配線を配置できる。オフ側FETのゲート電極は高周波信号としてGND電位であるので、ドレイン電極−ソース電極間の高周波信号の漏れを防止でき、交差部のポリイミドの配置と併せてスイッチMMICの歪特性を大幅に向上できる。

(もっと読む)

スイッチ集積回路装置およびその製造方法

【課題】高周波スイッチMMICにおいてD型HEMTとE型HEMTを同一基板に形成する場合、E型HEMTのゲート電極を形成する動作領域の半導体層を所定の深さまでエッチングし、異なるピンチオフ電圧を実現している。しかし、動作領域のエッチングは数nmの精度を必要とするため、歩留りが悪い問題があった。

【解決手段】AlGaAs層とInGaP層を繰り返し積層した第1〜第4ノンドープ層を有するエピタキシャル構造とし、D型HEMTの第2ゲート電極を第3ノンドープ層上に設け、E型HEMTの第1ゲート電極を第1ノンドープ層上に設ける。第1および第2ゲート電極はPt埋め込みゲート構造とし、Ptの蒸着厚みとノンドープ層の厚みを最適化しそれぞれのHEMTのピンチオフ電圧値を得る。また、プラズマダメージを受けた第4ノンドープ層を除去し、埋め込み部の端部が表面において尖った形状になることを防止し、耐圧を向上させる。

(もっと読む)

1 - 20 / 24

[ Back to top ]