Fターム[5F102HC24]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453) | 合金化、シリサイド化 (42)

Fターム[5F102HC24]に分類される特許

1 - 20 / 42

半導体装置

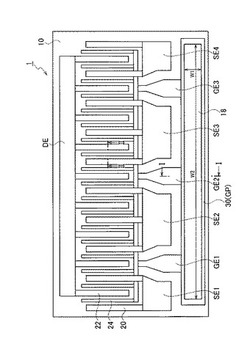

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

化合物半導体装置の製造方法

【課題】高い信頼性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層1上に、高融点金属を含む第1の導電膜3を形成する。第1の熱処理を行うことにより、第1の導電膜3と窒化物半導体層1とを反応させて高融点金属の窒化物層4を形成すると共に、窒化物半導体層1の表面に窒素空孔を生じさせる。第1の導電膜2上に、Alを含有する第2の導電膜3を形成する。第2の熱処理を行うことにより、第2の導電膜3中のAl原子を窒化物半導体層1の表面まで拡散させる。

(もっと読む)

化合物半導体装置、および化合物半導体装置の製造方法

【課題】ソース電極およびドレイン電極の表面モフォロジーおよび延性を向上させて耐圧を向上させ、オン抵抗の増加を抑制した化合物半導体装置、その製造方法を提供する。

【解決手段】化合物半導体装置1は、ソース領域21およびドレイン領域25が形成される化合物半導体層10(第2化合物半導体層12)と、ソース領域21およびドレイン領域25にそれぞれ対応して形成されたソース電極22およびドレイン電極26とを備える。ソース領域21およびドレイン領域25は、化合物半導体層10に対してオーミック性を有する領域形成用オーミック金属によって形成され、ソース電極22およびドレイン電極26は、領域形成用オーミック金属20r、24rを除去した領域へ新たに形成されソース領域21およびドレイン領域25に対してオーミック性を有する電極形成用オーミック金属22m、26mによって形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電流コラプスの小さな窒化物半導体デバイス用のショットキ電極を提供する。

【解決手段】窒素を含む3−5族化合物の半導体層と、前記半導体層に接して前記半導体層より上層に形成された導電体層と、を備えた半導体装置であって、前記導電体層は、2種以上の金属層が積層された積層金属層が合金化されて形成された合金であり、前記合金の仕事関数は、合金化前に前記半導体層に接していた金属の仕事関数より大きい半導体装置が提供される。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】信頼性を向上できる炭化珪素半導体装置の製造方法および炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置の製造方法は、以下の工程を備えている。まず、主面110aを含む炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の主面110aにシリコンをドーピングして、炭化珪素半導体層に110おいてシリコンがドーピングされていない領域よりもシリコン濃度の高い高濃度領域115が形成される。そして、高濃度領域115と接する位置に、シリコンと化合物を生成する材料を含む金属層143、144が形成される。そして、金属層143、144を熱処理して、化合物を含む電極が形成される。

(もっと読む)

化合物半導体装置及びそれを用いたドハティ増幅器

【課題】 バックオフ領域で動作しているときの利得を抑制することができ、ピーク増幅器に好ましく適用され得る化合物半導体装置を提供する。

【解決手段】 化合物半導体材料からなる下側電子走行層(3)の上に、n型にドーピングされ、下側電子走行層よりも電子親和力の小さな化合物半導体材料からなる下側電子供給層(4)が配置されている。下側電子供給層の上に、該下側電子供給層よりもドーピング濃度が低いか、またはノンドープの化合物半導体材料からなる上側電子走行層(5)が配置されている。上側電子走行層の上に、該上側電子走行層よりも電子親和力の小さなn型化合物半導体材料からなる上側電子供給層(7)が配置されている。上側電子供給層の上に、相互に離隔して配置され、下側電子走行層及び上側電子走行層にオーミックに接続されるソース電極及びドレイン電極が配置されている。ソース電極とドレイン電極との間の、上側電子供給層の上に、ゲート電極が配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】金属膜と絶縁膜との反応物の生成を抑制し、良好な電気的特性を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10は、基板11と、半導体層12と、絶縁膜13と、保護膜15と、ソース電極21と、ドレイン電極22と、ゲート電極23と、を備える。半導体装置10は絶縁膜13の少なくとも上面を覆うように形成された保護膜15を備えることによって、ソース電極21とドレイン電極22とに含まれるアルミニウムと絶縁膜13とが反応することを抑制することができ、電極の抵抗増加、電流コラプスの増加を抑え、良好な電気的特性を備える。

(もっと読む)

半導体素子の製造方法

【課題】電極形成工程を複雑化することなく、BeO膜を除去し優れた接合性を有するp側電極を形成することが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法によれば、AuBe層5を有するp側電極18、18a、18bの表面にオーミック特性付与時の熱により生成されるBeOをエッチングにより除去するため、電極形成工程を複雑化することなく、優れた接合性を有するp側電極18、18a、18bを形成することができる。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜に起因する問題を排除し、微細化に適した電界効果トランジスタを含む半導体装置を提供する。

【解決手段】半導体で形成されるチャネル領域102と、チャネル領域102上に形成されるゲート電極310と、チャネル領域102を挟んで両側に形成される同一導電型を有するソース領域210およびドレイン領域220とを具備する電界効果トランジスタを含む半導体装置であって、ゲート電極320が金属原子を含有する導電体によって形成され、チャネル領域102の少なくとも一部とゲート電極310が接触しており、チャネル領域102と、ソース領域210およびドレイン領域220が異なる導電型を有することを特徴とする半導体装置。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法

【課題】本発明は、半導体デバイスの製造コストを低減するために、GaNと化学組成の異なる異種基板にGaN薄膜が強固に貼り合わされているGaN薄膜貼り合わせ基板およびその製造方法、ならびに、GaN薄膜上に形成されている少なくとも1層のGaN系半導体層を含むGaN系半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN薄膜貼り合わせ基板1の製造方法は、GaNバルク結晶10にGaNと化学組成の異なる異種基板20を貼り合わせる工程と、異種基板20との界面から0.1μm以上100μm以下の距離を有する面10tでGaNバルク結晶10を分割して異種基板20上にGaN薄膜10aを形成する工程とを含み、GaNバルク結晶の貼り合わせ面の最大表面粗さRmaxが20μm以下であることを特徴とする。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】 本発明が解決しようとする課題は、窒化物半導体電界効果トランジスタにおいて、しきい電圧の制御が可能なエンハンスメント形の動作を得ることである。

【解決手段】 結晶方位の+c方向にAlxGa1−xN層、GaN層、AlyGa1−yN層の順に積層されており、x≧yにすることにより空乏化しているダブルヘテロ構造からなるチャンネルをゲート部に有することを特徴とする窒化物半導体電界効果トランジスタによって解決される。

(もっと読む)

集積回路装置

【課題】D型FETとE型FETを同一基板に集積化する場合、各ゲート電極を半導体層の異なる深さに設けて異なるピンチオフ電圧を実現している。しかし、半導体層のエッチングは数nmの精度を必要とするため歩留りが悪く、また複数の半導体層の選択エッチングを行う場合は、コストが高くなる問題があった。

【解決手段】D型FETとE型FETのゲート電極を、同一半導体層の同一平面上に蒸着する。また蒸着金属の最下層をPtとして一部を半導体層に埋め込み、D型FETとE型FETの埋め込み深さを異ならせる。E型FETのゲート電極はPt蒸着膜厚を100〜110Å以上で、埋め込み部の底部を第2電子供給層内の障壁層内に近い部分に位置させる。D型FETのゲート電極はPt蒸着膜厚を40〜60Åとする。これにより、何れのFETも所定のピンチオフ電圧でそのばらつきを大幅に低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を完全に埋め込むことが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に形成されたゲート電極2と、上記ゲート電極2の両側で上記半導体基板1上に配設されたソースドレイン電極3と、上記各ソースドレイン電極3間に塗布され、上記ゲート電極2を埋め込む埋め込み材4とを備えた半導体装置において、上記各ソースドレイン電極3の上記半導体基板1の表面から上端までの高さを、上記ゲート電極2の上記半導体基板1の表面から上端までの高さより高くした構成とする。

(もっと読む)

半導体装置

【課題】ダイオード内蔵型の接合FETにおいて、低いゲートバイアスでもブロッキング状態を維持でき、かつ大きな飽和電流を実現する。

【解決手段】n+SiC基板10をドレイン層、ドレイン層に接するn−SiC層11をドリフト層、ドリフト層上に形成されたn+SiC層12をソース層、ソース層からドリフト層の所定深さまでトレンチ溝を形成してドリフト層の一部をチャネル領域とし、トレンチ溝を充填するp型多結晶Siをゲート領域とする接合FETにおいて、チャネル片側のゲート領域をソース電極と短絡させてダイオードのpエミッタとする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】トレンチ構造のJ−FETが形成されるセル領域の一部に、ダイオードを内蔵する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】炭化珪素半導体で構成されたN+型ドレイン層11、N−型ドリフト層12およびN+型ソース層13が下から順に配置されている半導体基板1と、ソース層13の表面からドリフト層12に到達する深さのトレンチ14の側面14aに沿って配置されたP型ゲート層15と、トレンチ14の内部でゲート層15を覆う絶縁膜17と、ソース層13と電気的に接続されたソース電極19とを備える炭化珪素半導体装置において、少なくともトレンチ14の内部もしくは真下に、ソース電極19と電気的に接続され、ドリフト層12と接合してダイオード6を構成するショットキー電極18もしくはP型層のダイオード構成部を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下におけるオーミック電極の十分な信頼性を確保しながら、高湿度環境下におけるオーミック電極の信頼性を向上させる。

【解決手段】半導体装置を、基板11と、n型半導体層3又はアンドープ半導体層と、オーミック電極12,13とを備え、オーミック電極12,13が、n型半導体層3又はアンドープ半導体層上に形成されたタンタル層9と、タンタル層9上に形成されたアルミニウム層10と、アルミニウム層10上に形成され、タンタル,ニッケル,パラジウム,モリブデンのうちのいずれか1つの材料からなる金属層9とを備えるものとする。

(もっと読む)

ミリメートル波動作のための窒化物ベースのトランジスタ

【課題】ミリメートル波動作のために設計された広バンドギャップのトランジスタの提供。

【解決手段】第III族窒化物チャネル層と;第III族窒化物チャネル層の上のスペーサ層と;第III族窒化物チャネル層の上にあり、かつ30GHzを超える周波数において印加される電圧に応じてチャネル層の伝導率を変調するのに十分なゲート長を有するゲート接点と;ゲート接点と電気的に接続され、スペーサ層を横断してドレイン接点に向かう方向に少なくとも約0.1μm延びる下部フィールドプレートと;第III族窒化物チャネル層の上のソース接点およびドレイン接点とを含み、少なくとも30GHzの周波数における動作時に約5W/mmより大きな電力密度を示すことを特徴とする電界効果トランジスタ。

(もっと読む)

1 - 20 / 42

[ Back to top ]