Fターム[5F110EE14]の内容

Fターム[5F110EE14]の下位に属するFターム

三層以上 (1,118)

Fターム[5F110EE14]に分類される特許

3,661 - 3,665 / 3,665

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

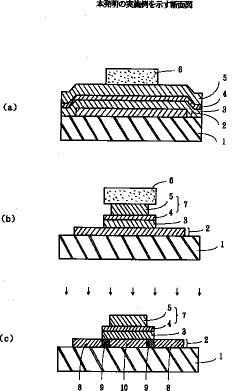

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

積層金属配線及び薄膜トランジスタ基板、並びにそれらの製造方法

【課題】 IC等の半導体装置や、表示装置に用いられるTFT基板で使用される、Alを含む積層配線の信頼性を高める。

【解決手段】 上層の金属層22を下層のAl又はAlを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させる。この積層配線は、エッチングによりこれを作製する際に、上層の金属層22よりも下層のAl又はAlを含む合金の材料層21の方のエッチング速度を大きくして、Al又はAlを含む合金の材料層21のサイドエッチングを多くし、上層の金属層22を下層のアルミニウム又はアルミニウムを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させることで作製できる。

(もっと読む)

3,661 - 3,665 / 3,665

[ Back to top ]