Fターム[5F140BJ03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 最下層材料 (3,069)

Fターム[5F140BJ03]の下位に属するFターム

Fターム[5F140BJ03]に分類される特許

41 - 47 / 47

半導体装置

【課題】 従来の半導体装置では、過電圧から素子を保護するために設けられたN型の拡散領域が狭く、ブレークダウン電流が集中し、保護用のPN接合領域が破壊されてしまうという問題があった。

【解決手段】 本発明の半導体装置では、基板2とエピタキシャル層3とにP型の埋込拡散層4が形成されている。N型の埋込拡散層5が、P型の埋込拡散層4と重畳するように形成され、素子形成領域の下方に過電圧保護用のPN接合領域19が形成されている。PN接合領域19のブレークダウン電圧は、ソース−ドレイン間のブレークダウン電圧よりも低い。この構造により、ブレークダウン電流が、PN接合領域19に集中することを防止し、過電圧から半導体素子を保護することができる。

(もっと読む)

半導体装置

【課題】 従来の半導体装置では、過電圧から素子を保護するために設けられたN型の拡散領域が狭く、ブレークダウン電流が集中し、保護用のPN接合領域が破壊されてしまうという問題があった。

【解決手段】 本発明の半導体装置では、基板2とエピタキシャル層3とに渡りN型の埋込拡散層4が形成されている。P型の埋込拡散層5が、N型の埋込拡散層4上面の広い領域に渡り形成され、過電圧保護用のPN接合領域17が形成されている。P型の拡散層6が、P型の埋込拡散層5と連結するように形成されている。PN接合領域17のブレークダウン電圧は、ソース−ドレイン間のブレークダウン電圧よりも低い。この構造により、ブレークダウン電流の集中を防止し、過電圧から半導体装置を保護することができる。

(もっと読む)

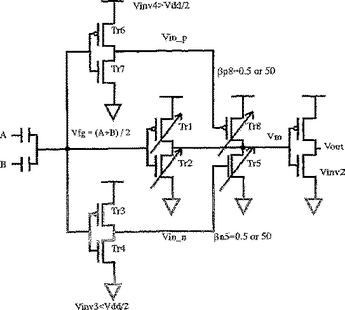

スピン依存伝達特性を有するトランジスタを用いた再構成可能な論理回路

不揮発に再構成可能な論理回路を構成する。スピンMOSFETを用いたCMOS構成による再構成可能な論理回路である。スピンMOSFETであるTr1、Tr2、Tr5、Tr8の磁化状態によりそれぞれのトランジスタの伝達特性を変化させることでAND/OR/XOR/NAND/NOR/XNOR/“1”/“0”の全2入力対称関数が再構成可能である。不揮発かつ少素子数で論理機能を構成できるため、チップ面積の縮小化が可能であり、高速・低消費電力動作が期待できる。  (もっと読む)

(もっと読む)

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

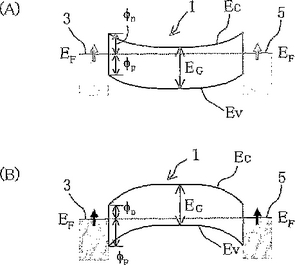

ゲート電圧VGSの印加によって、強磁性ソースにおける金属的スピンバンドによるショットキー障壁幅が減少し、この金属的スピンバンドからのアップスピン電子がチャネル領域にトンネル注入される。このとき強磁性ソース3aの半導体的スピンバンドによるエネルギー障壁により非磁性コンタクト3bからダウンスピン電子は注入されない。すなわち、強磁性ソース3aからはチャネル層へアップスピン電子のみが注入される。強磁性ソース3aと強磁性ドレイン5aとが平行磁化の場合では、アップスピン電子は強磁性ドレインの金属的スピンバンドを伝導してドレイン電流となるが、反平行磁化を持つ場合では、アップスピン電子は強磁性ドレイン5aにおける半導体的スピンバンドによる高さΔEcのエネルギー障壁よって強磁性ドレイン5aを伝導することができない。 上記動作原理のMISFETに基づき、高性能・高集積密度の不揮発性メモリを構成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートの空乏化問題の解消と共に、仕事関数の調整が容易な金属シリサイドのみからなるゲート電極を備え、既存プロセスとのインテグレーション性が高い、コスト的にも優位性がある電界効果トランジスタからなる半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板1と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極19と、前記ゲート電極19を挟んでエレベーテッド構造を有するソース・ドレイン8とからなる半導体装置の製造方法であって、前記ゲート電極19を金属シリサイド化する工程を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 従来の半導体装置の製造方法では、LOCOS酸化膜を形成した後、LOCOS酸化膜のバーズビークを用い、ドレイン拡散層を形成するので、ドレイン拡散層の位置精度が悪いという問題があった。

【解決手段】 本発明の半導体装置の製造方法では、エピタキシャル層4上面にポリシリコン膜9及びシリコン窒化膜10を堆積する。LOCOS酸化膜14を形成する領域にポリシリコン膜9及びシリコン窒化膜10が残存するようにパターニングする。そして、ポリシリコン膜9及びシリコン窒化膜10の段差をアライメントマークとして利用し、ドレイン領域としての拡散層11を形成する。その後、LOCOS酸化膜14を形成する。この製造方法により、LOCOS酸化膜の形状に影響を受けることなく、拡散層11を位置精度良く形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

41 - 47 / 47

[ Back to top ]