Fターム[5F152CE39]の内容

再結晶化技術 (53,633) | 被結晶化層 (7,497) | 元素が導入されたもの(結晶化直前の状態) (601) | 導入領域 (10)

Fターム[5F152CE39]に分類される特許

1 - 10 / 10

半導体装置

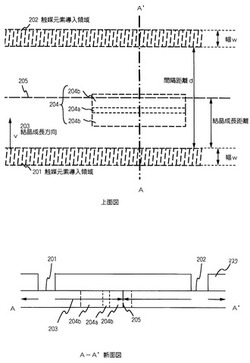

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

半導体装置の作製方法

【課題】高温(600℃以上)の加熱処理回数を低減し、さらなる低温プロセ

ス(600℃以下)を実現するとともに、工程簡略化及びスループットの向上を

実現することを課題とする。

【解決手段】本発明は結晶構造を有する半導体膜へマスク106bを用いて希ガ

ス元素(希ガスとも呼ばれる)を添加した不純物領域108を形成し、加熱処理

により前記不純物領域108に半導体膜に含まれる金属元素を偏析させるゲッタ

リングを行った後、前記マスクを用いてパターニングを行い、結晶構造を有する

半導体膜からなる半導体層109を形成する。

(もっと読む)

半導体基板、及びその製造方法

【課題】DSB基板を用いてHOT構造の半導体基板を作製するに際し、その機能性基板の、互いに異なる結晶方位を有する結晶領域の境界における結晶欠陥の発生を抑制し、本来的な実用に足る前記HOT構造の半導体基板を提供する。

【解決手段】第1の結晶方位を有するシリコン支持基板と、このシリコン支持基板上に直接的に形成され、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第1の結晶領域と、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第2の結晶領域とを有するシリコン機能性基板とを具えた半導体基板において、前記シリコン機能性基板の、前記第1の結晶領域及び前記第2の結晶領域の境界に、少なくとも前記シリコン支持基板の主面にまで達するような溝部を形成する。

(もっと読む)

多結晶シリコン層、多結晶シリコン層の製造方法、及び平板表示装置

【課題】結晶粒の大きさや結晶粒界の分布が均一であり、薄膜トランジスタを形成した際に優秀な特性が得られる多結晶シリコン層、多結晶シリコン層の製造方法、及び平板表示装置を提供する。

【解決手段】基板上に非晶質シリコン層120を形成する段階と、非晶質シリコン層120の所定領域が露出するように第1パターン層130を形成する段階と、第2パターン層140を形成する段階と、第2パターン層140上に金属触媒層150を形成する段階と、基板を熱処理することにより、金属触媒が非晶質シリコン層の所定領域に拡散してシードを形成し、シードは非晶質シリコン層120の所定領域を少なくとも幅が3.5μm以上であるシード領域170に結晶化し、シード領域170の結晶性が成長して、非晶質シリコン層120を結晶化領域190に結晶化する段階と、を含むことを特徴とする。

(もっと読む)

薄膜トランジスタを備えた半導体装置及びその製造方法

【課題】 従来よりも総工程数を減少でき、且つ動作特性及び信頼性を改善することができる半導体装置及びその製造方法を提供することにある。

【解決手段】 基板10に直接または下地膜12を介してアイランド状に形成された、活性層として機能する半導体膜45と、この半導体膜45内に形成された一対のソース・ドレイン領域20a及び20bとを備える。一対のソース・ドレイン領域20a及び20bは、半導体膜45のソース・ドレイン領域20a及び20b以外の部分よりも薄くされており、その厚さの差が10オングストローム〜100オングストロームの範囲内に設定されている。

(もっと読む)

表示装置の製造方法および表示装置

【課題】高速動作が可能な機能回路をも同一基板上に形成され得る、従来よりも高性能な駆動回路一体型表示装置を高い効率で製造する方法を提供する。

【解決手段】本発明の表示装置の製造方法は、(a)基板の上に非晶質半導体膜12を形成する工程と、(b)酸素を含む雰囲気下で、非晶質半導体膜の一部の領域に光線を照射し、当該光照射された領域の非晶質半導体膜を完全に溶融し、結晶化することによって結晶質半導体膜13を部分的に形成する工程と、(c)非晶質半導体膜の少なくとも上層部分を溶融するエネルギー密度の光線を結晶質半導体膜および非晶質半導体膜に照射することによって、結晶質半導体膜よりも上面が平坦な第1の結晶質半導体膜16を形成するとともに、非晶質半導体膜が結晶化された第2の結晶質半導体膜17を形成する工程と、工程(b)と(c)との間に、結晶質半導体膜および非晶質半導体膜の上面に形成された酸化膜をエッチングする工程とを包含する。

(もっと読む)

微小構造体、およびその作製方法

【課題】シリコンウエハ上に形成されるものではない微小構造体、および微小構造体を有するマイクロマシンを提供する。また、微小構造体およびマイクロマシンの作製方法を提供する。

【解決手段】ガラスなどの絶縁物からなる基板101の上に第1の構造層103を成膜する。この構造層は結晶化を促進する金属元素を用いて熱結晶化またはレーザ結晶化された多結晶シリコンを用いる。この多結晶シリコンは一般的な多結晶シリコンと異なり結晶粒界で共有結合が途切れることなく連続しており、破壊応力が高く構造層に好適となる。続いて第1の構造層の上に犠牲層104を、さらに第2の構造層105を成膜する。第2の構造層は第1の構造層と同様な材料、同様な結晶構造を有するものを用いることができる。その後犠牲層を除去すれば第2の構造層は梁構造となり、微小構造体が得られる。

(もっと読む)

半導体装置および電子機器

【課題】優良な多結晶薄膜半導体装置を比較的低温で製造する。

【解決手段】多結晶半導体膜形成後、希ガス元素イオンを半導体膜に注入する。その後溶融結晶化を行う。

(もっと読む)

半導体装置の作製方法

【課題】ゲート電極や配線を低抵抗な金属膜を用いて形成することにより、大面積なデバイスにも対応できる半導体装置の作製方法を提供する。

【解決手段】基板上にアルミニウムを主成分とする第1の導電層を形成し、前記第1の導電層上に当該第1の導電層と異なる材料からなる第2の導電層を形成し、前記第1の導電層及び前記第2の導電層をパターニングしてゲート電極を形成することを特徴とする。また、前記第1の導電層は、炭素と、クロム、タンタル、タングステン、モリブデン、チタン、シリコン、ニッケルのいずれか一又は複数を含有していることを特徴とする。前記第2の導電層は、クロム、タンタル、タングステン、モリブデン、チタン、ニッケルまたはこれらの窒化物のいずれか一又は複数からなることを特徴とする。

(もっと読む)

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

1 - 10 / 10

[ Back to top ]