Fターム[5F152FF50]の内容

Fターム[5F152FF50]に分類される特許

1 - 11 / 11

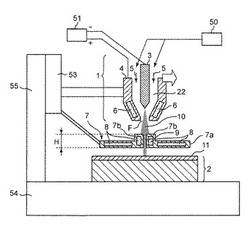

熱プラズマ処理装置

【課題】基材の表面近傍をごく短時間だけ均一に高温熱処理するに際して、基材の所望の被処理領域全体を短時間で処理することのできる熱プラズマ処理装置を提供する。

【解決手段】内部に不活性ガス5を流す熱プラズマノズル1と基材2との間に配置されたノズルカバー7に線状スリット9が設けられ、熱プラズマノズルに電力を供給して、噴出口Fから熱プラズマジェット10を発生させ、線状スリット9を通過したエネルギー束が基材2の表面に作用し、基材2の表面近傍11を熱処理する。

(もっと読む)

半導体製造方法

【課題】 ゲルマニウム(Ge)半導体を自己組織的に実現するGe半導体製造方法。

【解決手段】 シリコン(Si)とゲルマニウム(Ge)からなるSiGe薄膜を融液成長により固化させ、結晶化されたSiGe薄膜中に自己組織的に出現したGe偏析に起因するGe高濃度構造を形成する。さらに酸化濃縮技術を利用してGe濃度を高めることを特徴としたGe半導体製造方法。

(もっと読む)

光電変換装置の作製方法

【課題】限りある資源を有効活用しつつ、優れた光電変換特性を有する光電変換装置を安全に提供することを課題の一とする。

【解決手段】単結晶半導体基板中に脆化層を形成し、且つ単結晶半導体基板の一表面上に第1の不純物半導体層、第1の電極、及び絶縁層を形成し、絶縁層と支持基板を密着させて単結晶半導体基板と支持基板を貼り合わせた後、脆化層において単結晶半導体基板を分離させて第1の単結晶半導体層を有する積層体を形成し、第1の単結晶半導体層上に第1の半導体層及び第2の半導体層を形成し、固相成長により、第1の半導体層及び第2の半導体層の結晶性を向上させて、第2の単結晶半導体層を形成し、第2の単結晶半導体層上に、第1の不純物半導体層とは逆の導電型の第2の不純物半導体層を形成し、第2の不純物半導体層上に第2の電極を形成する。

(もっと読む)

半導体膜の製造方法、半導体素子の製造方法、電気光学装置、電子機器

【課題】熱プラズマジェット結晶化技術を更に改良し、従来よりも更に均一性を高めて半導体膜の結晶化を行うこと。

【解決手段】半導体膜の製造方法であって、基板(106)上に半導体膜(104)を形成する第1工程と、熱プラズマ(103)を、上記半導体膜の表面と平行な第1軸に沿って相対的に移動させながら上記半導体膜に当てる第2工程と、を含み、上記第2工程は、上記熱プラズマの噴出孔(107)の上記第1軸方向の距離Φを上記熱プラズマと上記基板の相対的な移動速度vで除した値であるΦ/vが5ミリ秒以上40ミリ秒以下、かつ、上記熱プラズマを発生させる電極部(102)と上記基板との相互間の距離Dが2mm以上15mm以下、の条件下で行われる。

(もっと読む)

ジュール加熱による急速熱処理時にアーク発生を防止する方法(METHODOFPREVENTINGGENERATIONOFARCDURINGRAPIDANNEALINGBYJOULEHEATING)

本発明は、熱処理を必要とする材料、絶縁層及び導電層の混合構造で、前記導電層に電界を印加してジュール加熱により瞬間的に発生する高熱により前記熱処理を必要とする材料の所望する部位を急速熱処理する際に、前記熱処理を必要とする材料と導電層との電位差を前記絶縁層の絶縁破壊電圧よりも低く設定することで、熱処理中に絶縁層の絶縁破壊によるアーク発生を防止することができる急速熱処理方法に関する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高精度の抵抗値を有する抵抗素子を得ることを目的とする。

【解決手段】シリコン基板11上に0.1〜0.5μmの間隔を設けて島状に酸化膜12を形成する工程と、フッ化水素酸溶液を用いたウェット処理を行なう工程と、酸化膜12を備えたシリコン基板11上にシランガスを用いた成膜温度520〜560℃の減圧CVD法によりアモルファスシリコン層14aを形成する工程と、温度890〜960℃、10〜15秒での熱処理を施す工程を含み、アモルファスシリコン層14aを単結晶シリコン層14bに構造変換し、単結晶シリコン層14bで抵抗素子を形成する。

(もっと読む)

薄膜トランジスタを備えた半導体装置及びその製造方法

【課題】 従来よりも総工程数を減少でき、且つ動作特性及び信頼性を改善することができる半導体装置及びその製造方法を提供することにある。

【解決手段】 基板10に直接または下地膜12を介してアイランド状に形成された、活性層として機能する半導体膜45と、この半導体膜45内に形成された一対のソース・ドレイン領域20a及び20bとを備える。一対のソース・ドレイン領域20a及び20bは、半導体膜45のソース・ドレイン領域20a及び20b以外の部分よりも薄くされており、その厚さの差が10オングストローム〜100オングストロームの範囲内に設定されている。

(もっと読む)

半導体装置の作製方法

【課題】低コストで信頼性の高い半導体装置の作製方法を提供する。

【解決手段】基板上に金属膜を形成し、前記金属膜に酸素を含む雰囲気中でプラズマ処理を行うことにより、前記金属膜の表面に金属酸化膜を形成し、前記金属酸化膜上に下地膜を形成し、前記下地膜上に薄膜トランジスタを有する素子層を形成し、前記素子層上に保護層を形成し、前記金属膜、前記金属酸化膜、前記下地膜、前記素子層、及び前記保護層を選択的に除去して、開口部を形成し、前記基板から前記下地膜、前記素子層、及び前記保護層を分離し、可撓性を有する第1及び第2のフィルムを用いて前記下地膜、前記素子層、及び前記保護層を封止し、前記基板付近でのプラズマの電子密度は1×1011cm−3以上1×1013cm−3以下であり、電子温度は0.5eV以上1.5eV以下である。

(もっと読む)

半導体装置の製造方法、製造装置ならびに電子機器

【課題】 低温プロセスで大面積の半導体基板の熱処理を品質良く行うことが可能な半導体装置の製造方法等を提供する。

を提供する。

【解決手段】 半導体装置の製造において、水素及び酸素の混合ガスを燃料とする長尺のガスバーナーの線状の火炎を熱源として基板上に成膜された半導体層を熱処理する工程を含む。かかる構成により、加熱と共に燃焼によって生じる水蒸気ガスを半導体層に付与することができ、再結晶化と薄膜半導体層のダングリングボンドを水素又は酸素によって終端して電荷のトラップを減少する。また、大型基板の熱処理が可能となる。

(もっと読む)

3次元半導体集積回路装置の製造方法および3次元半導体集積回路装置

【課題】開発期間を短縮でき、製造コストを低減でき、しかも、回路特性を安定化させることができ、さらに、製造工程を簡略化でき、集積回路の損傷を防ぐことができる3次元半導体集積回路装置の製造方法および3次元半導体集積回路装置を提供する。

【解決手段】第1の半導体基板とこの第1の半導体基板に形成された第1の半導体集積回路とを有する第1の半導体集積回路基板10上に、絶縁膜15を介して非晶質シリコン層を形成する。非晶質シリコン層の複数の部分を選択的に再結晶化して、複数の再結晶化領域34を含む多結晶シリコン層31を形成する。複数の再結晶化領域34と所定の位置関係を持つように、多結晶シリコン層31に第2の半導体集積回路を形成して、多結晶シリコン層31と第2の半導体集積回路とを有する第2の半導体集積回路基板30を作製する。

(もっと読む)

微粒子分散絶縁膜の製造方法、これを用いたメモリ素子、発光素子の製造方法及びメモリ素子、発光素子

【課題】ガラス等の基板を含む種々の基板上に作製することができるとともに、電荷保持ノード又はキャリアの発光再結合中心として作用する微粒子分散絶縁膜中の半導体微粒子の面密度が高く、かつ、膜厚方向で広範囲にわたって均一な面密度を有する微粒子分散絶縁膜の製造方法、これを用いたメモリ素子、発光素子の製造方法及びメモリ素子、発光素子を提供する。

【解決手段】微粒子分散絶縁膜15の製造方法は、基板11上に半導体成分を過剰に含む組成の絶縁膜150を形成する工程と、該絶縁膜150をプラズマジェット50を用いたアニールにより前記半導体成分を相分離させて分散半導体微粒子152を形成する工程と、からなる。

(もっと読む)

1 - 11 / 11

[ Back to top ]