Fターム[5F152NP07]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413) | InAs (4)

Fターム[5F152NP07]に分類される特許

1 - 4 / 4

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

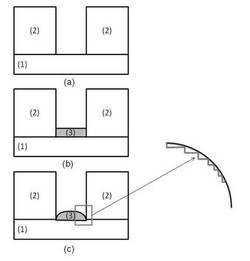

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

半導体ウェハ

【課題】GaAs基板からの能動層への転位の伝播を抑止する半導体結晶基板の構造を提供すること。

【解決手段】GaAs基板1と能動層40との間に、平面内にInAs核をドット状(島状)に形成し、その上にInAs核が埋まる程度にIII−V族化合物半導体のバッファ層20を成長した構造を設ける。

(もっと読む)

1 - 4 / 4

[ Back to top ]