Fターム[5H740GG03]の内容

Fターム[5H740GG03]に分類される特許

1 - 5 / 5

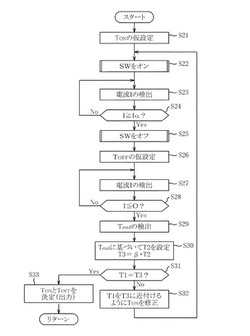

直流電源装置

【課題】リアクトルの出力を短絡するスイッチ素子の導通・遮断タイミングを適正に設定して高調波の発生を抑制することのできる直流電源装置を提供する。

【解決手段】スイッチ素子の導通タイミングから制御周期の初期において前記リアクトルからの出力電流が零である第1のオフ期間を求めると共に、前記スイッチ素子を遮断した後に前記リアクトルから出力される電流が零となるタイミングから前記周期の終期において前記リアクトルからの出力電流が零である第2のオフ期間を求め(第1の手段)、第2のオフ期間に基づいて設定される目標オフ期間に前記第1のオフ期間が近付くように前記スイッチ素子の導通タイミングを修正して前記第1の手段を再起動して、前記第1のオフ期間と前記目標オフ期間とが一致するように前記スイッチ素子の導通タイミングを決定する(第2の手段)。

(もっと読む)

制御モータ駆動装置

【課題】本発明は上記課題に鑑み、インバータ回路におけるスイッチング素子の出力電流に発生するノイズを同期的に低減させ、インバータ回路によって駆動される制御モータの誤作動を有効に防止し得る制御モータ駆動装置の提供を目的とする。

【解決手段】制御モータ駆動装置100を構成するインバータ回路240は、ドライブ回路141と複数のスイッチ回路242a〜242fと電流検出回路143とを備えている。そして、インバータ回路240に配備されるそれぞれのスイッチ回路242a〜242fは、ゲートGに接続される調整抵抗Rga〜Rgfと、エミッタE−コレクタC間に接続される帰還ダイオードD1a〜D1fと、ゲートG−エミッタE間に接続される吸収ダイオードD2a〜D2fとを備えるスイッチング素子Tra〜Trfから構成されている。

(もっと読む)

交流電源装置

【課題】 交流入力波形のゼロクロス点を検出してその位相を求め、この位相から基準波形を生成して、この基準波形と交流入力波形の差分電圧を、交流入力波形に加算するようにした交流電源装置において、ゼロクロス点付近に水平部分がある交流入力波形では、ゼロクロス点を正確に検出することができないので、正確な基準波形を生成することができなかったという課題を解決する。

【解決手段】 ゼロクロス点を検出する位相検出部の前にインダクタあるいはフィルタを設け、このインダクタ/フィルタでゼロクロス点付近の波形を鈍らせて傾斜を付けるようにした。ゼロクロス点付近で水平部分を有する波形でも正確にゼロクロス点を検出でき、正確な基準波形を生成することができる。

(もっと読む)

負荷駆動装置及び負荷駆動方法

【課題】 EMIノイズのピークレベルを増大させずに、かつ、ビートノイズの発生を抑制して、2個1組の負荷を制御する。

【解決手段】 2個1組の第1、第2の負荷31、32を駆動する第1、第2の駆動手段21、22と、駆動手段21、22を制御する第1、第2の制御信号を出力する制御手段23とを設け、制御手段23に周期的に変化する第1、第2のPWM制御信号のキャリア周波数fc1、fc2を決定するキャリア周波数決定手段44を設け、キャリア周波数fc1、fc2の平均周波数、キャリア周波数fc1、fc2の周期的な変化を示す周波数変化波形の振幅及び周期を等しくし、かつ、キャリア周波数fc1、fc2の周波数変化波形の位相差を180度とする。

(もっと読む)

トライアックのトリガを制御するシステムおよび方法

この発明は、トライアックのゲートへの単一の短い期間のパルスであらゆる力率の負荷を動作させることにより、トライアックを制御しトリガするシステムに関する。単一のコンパレータ(CP1)を使用するために、また、電流レベル(Ic)で制限することなく動作させるために、トライアックを制御しトリガするシステムが予見され、前記トライアックはゲートを備え、かつ、負荷に接続され、ゲートは、制御ユニット4に接続され、 制御ユニットは、回路電圧Vacを負荷に印加して電流Icを流すためにトライアックを動作させ、システムは、ゲート電圧検出ユニット(1)、制御ユニット(4)、制御ユニット(4)に接続のゲート電圧検出ユニット(1)を備え、制御ユニットはゲート電圧限界値(+LIMIT,−LIMIT)を確立し、トライアックの導通を維持するためゲートにパルスを発生させ、ゲートでのパルスは、前記電圧限界値と、ゲート測定電圧との比較から発生され、制御ユニットは、Icを測定し、Icに比例して電圧限界値を調節する。

(もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]