Fターム[5J014CA14]の内容

Fターム[5J014CA14]の下位に属するFターム

サブキャリア (4)

Fターム[5J014CA14]に分類される特許

1 - 11 / 11

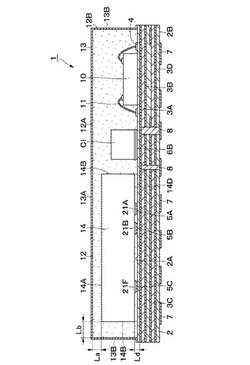

送信モジュール

【課題】 コアアイソレータ素子の挿入損失の増加を抑制した、送信モジュールを提供する。

【解決手段】 回路基板2は、グランドパターン3A〜3Dを備えた多層基板である。回路基板2には、電力増幅器10およびコアアイソレータ素子14が実装される。電力増幅器10およびコアアイソレータ素子14は、樹脂層12によって覆われる。樹脂層12の表面にはシールド層13が設けられる。コアアイソレータ素子14の天面14Aと、天面14Aと対向するシールド層13の天面シールド層13Aとの間隔、コアアイソレータ素子14の側面と、この側面と対向するシールド層13の側面シールド層との間隔を、所定の距離だけ離間して、コアアイソレータ素子14による挿入損失の増加を抑制する。

(もっと読む)

マイクロ波回路

【課題】高利得の増幅器の発振を防止することができるようにする。

【解決手段】キャビティ2,3の外側に配置されており、一方の端子が増幅器5のバイアス端子5cと接続され、他方の端子6aが増幅器4の入力端子4aと同じ側に配置されているローパスフィルタ6と、パッケージ1の接地面1bと接続されている状態で、パッケージ1及びローパスフィルタ6の周囲を覆っている導電性ケース7と、パッケージ1の上面1aに配置され、パッケージ1の接地面1bと電気的に接続されている導電性のキャップ8と、導電性ケース7の上面7aと導電性のキャップ8を接続している導電性の弾性体9とを備える。

(もっと読む)

高周波パッケージ

【課題】使用周波数によるキャビティ寸法の制約なく2倍波の漏洩を抑圧できる高周波パッケージを得ること。

【解決手段】出力整合回路4と高周波パッケージ1の出力端子2との間に、使用周波数の2倍波に対する1/4波長型吸収体を配置し、出力整合回路4の出力端と出力端子2との間を2倍波のカットオフブロックで覆ったマイクロトリップ線路で接続し、1/4波長型吸収体を構成する抵抗膜6に、マイクロストリップ線路7を覆う2倍波カットオフブロック8の外周が密着した状態で貫通する貫通穴を設けてある。

(もっと読む)

回路基板

【課題】信号の周波数が高くなっても信号に歪みが発生することを抑制できると共に、U字型に容易に曲げることができる回路基板を提供する。

【解決手段】回路基板10は、電子部品が実装される基板部12,14、及び、基板部12,14を接続する接続部16を有し、かつ、可撓性材料からなる複数のシートが積層されてなる。配線導体32b,32cは、接続部16内に設けられ、基板部12,14との間において延在している。グランド導体38は、積層方向から平面視したときに配線導体32b,32cと重なるように、接続部16内に設けられている。グランド導体38は、電子装置への搭載のために接続部16が湾曲させられた場合に、積層方向において回路基板10の中心に位置する中心面Cよりも、内側に位置している。

(もっと読む)

半導体チップ実装基板

【課題】半導体チップを埋め込んだマルチポートの半導体チップ実装基板において、ポート間のアイソレーションを向上させること。

【解決手段】この半導体チップ100の1辺の長さは約2.5mmであり、この長さは、目的の高周波の環状溝210内における環方向の波長の半分余りに相当している。この半導体チップ100の周囲には、空洞部220に半導体チップ100を搭載した後の残りの空間によって、平面視時の輪郭が略正方形のリング形状の環状溝210が形成されている。そして、この環状溝210の4隅にはそれぞれ、銀ペーストからなる柱状導体1が埋め込まれている。即ち、この柱状導体1は、上記の空洞部220の内壁面と上記の半導体チップ100の側壁面との間の隙間から形成される環状溝210の4隅に配置されており、半導体チップ100の裏面に配置される共通グランドの上に直接立脚している。

(もっと読む)

方向性結合器および半導体装置

【課題】方向性結合器を小型化することができる技術を提供する。

【解決手段】積層された複数の絶縁層と、前記複数の絶縁層それぞれの表面に所望のパターンで配線が形成された複数の配線層とを有する配線基板と、前記複数の配線層のうち、単一の配線層に形成された主線路(第1配線)11と、前記複数の配線層に亘って形成され、主線路11に沿って延在する延在部13a、13b、13cを備えた副線路(第2配線)12とを備える方向性結合器10であって、主線路11は屈曲部を有さず、副線路12は、主線路11の一方の側面側にコイル形状のループを成すように形成する。

(もっと読む)

メタマテリアルを用いた伝送線路の設計方法

無線、デジタルおよびマイクロ波アプリケーション用の高周波回路には、それらの信号線、配線およびパッケージングのインピーダンスに対する要求がある。これら信号線に用いる基板の設計および実施において、所望のインピーダンスを提供するためにメタマテリアルを用いることは有益である。このようなメタマテリアルは、用いられる絶縁体の実際の誘電率および透磁率とは異なる、修正された誘電率および透磁率を基板に与えるための手段を提供する。一例の実施形態では、基板がメタマテリアルとして構成される。よって、信号線のこれらメタマテリアルの特徴(aspects)を迅速かつ正確にモデリングする手段を備えることにより、費用がかかりかつ網羅的な繰り返しの実験的特性評価を行うことなく、回路、配線およびパッケージが設計および実施されるようにすることが望ましい。上掲の発明では、メタマテリアル構造の設計パラメータは、導電媒質、導電材料を取り囲む誘電体媒質、および導電媒質の所定の形状を特徴付ける入力パラメータに基づいて決定される。  (もっと読む)

(もっと読む)

マイクロ波回路装置

【課題】 マイクロ波集積回路基板の実装に関し、マイクロストリップ線路回路パターンの高密度配線を実現する。

【解決手段】 本発明によるマイクロ波集積回路基板実装構造は、表面にマイクロストリップ線路を備え、かつ裏面が導電性ベースプレートに固定された複数の誘電体基板間又は誘電体基板とそれに隣接する構造物との間隙に、誘電体基板と同一又は誘電体基板以上の誘電率をもった弾性材料を配置することで、波長短縮率を減少させ。誘電体基板上のマイクロストリップ線路回路パターンの高密度配線を実現するものである。

(もっと読む)

マイクロストリップ線路と、これを用いたマイクロ波装置

【課題】 衛星放送などの受信に用いられるマイクロ波装置において、損失の少ないマイクロストリップ線路を提供する。

【解決手段】 比誘電率が1以上のプリント基板11と、このプリント基板11の表面上に敷設されるとともにマイクロ波を導くストリップ線路13と、プリント基板11の裏面側とグランドプレーン14との間に設けられた空気層16とを備え、ストリップ線路13とプリント基板11と空気層16とグランドプレーン14で特性インピーダンスを形成する構成としたものである。これによりストリップ線路の損失を少なくすることができる。

(もっと読む)

伝送線路

【課題】従来のマイクロストリップ型の伝送線路においては中心導体および下面電極形成のための基板材料および誘電体材料の誘電率の影響を受け、線路伝搬の電磁波の速度が低下し、伝搬遅延時間が大きくなり、同時に線路周辺の浮遊容量も大となり線路の高速化と高周波特性に対して障害となっていた。このため、本発明はこのような誘電率の影響を受けない伝送線路の実現を目的としたものである。

【解決手段】基板およびその上に形成されている下面電極と中心導体とが空隙をもって配置し得るように支柱および横板で中心導体を支持する構造としている。この支持構造は高周波信号の伝搬、即ち、中心導体及びその近傍に発生する電磁場に影響をおよぼさないように配置される。あるいは、構造的強度を確保するために低誘電率の材料を中心導体周辺の空間に充填する方法としている。

(もっと読む)

ストリップ線路のプリント基板の保持構造

【課題】 コストダウン、および、取付け時の操作性の向上を図ることができるストリップ線路のプリント基板の保持構造を実現すること。

【解決手段】 プリント基板12に実装された給電ライン15Aは接地導体板13に対向している。略コの字状を有するスペーサ14が、プリント基板12と接地導体板13との間に介在して、この間隔を規制する。一対の接着シートが上下端面に貼着されたスペーサ14をプリント基板12および接地導体板13杆に配置する。スペーサ14の厚みを細かいレンジで制御することができる。部品点数を削減することができる。

(もっと読む)

1 - 11 / 11

[ Back to top ]