Fターム[5J023CB09]の内容

遅延要素を用いたフィルタ (1,075) | 目的 (151) | 特性改善・可変 (109) | 容量可変 (6)

Fターム[5J023CB09]に分類される特許

1 - 6 / 6

スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器

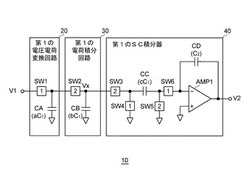

【課題】面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供する。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

(もっと読む)

AD変換装置

【課題】アナログイコライザの前置を不要とするAD変換装置を提供する。

【解決手段】Nビット分解能を有するM個(M≧N+3)の逐次比較型AD変換回路と制御回路とを備え、各逐次比較型AD変換回路(i)は、入力アナログ信号のサンプリング電圧Vs(i)に相当する電荷Q(i)を保持する可変容量キャパシタCv1〜Cvm−1と、各可変容量キャパシタの容量の変更に応じて、逐次比較型AD変換回路(i)〜(i+m−2)内の、容量が変更された可変容量キャパシタCv1〜Cvm−1の端子間に現れる係数乗算電圧Vm(i)〜Vm(i+m−2)と、サンプリングタイミングT(i+m−1)に対応するサンプリング電圧Vs(i+m−1)とに基づいて、前補正電圧Vd(i+m−1)を生成する電圧補正回路と、Nビットのデジタル出力を生成する逐次比較部とを備え、可変容量キャパシタの容量を変化させる容量制御部を備える。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

フィルタ回路および通信装置

【課題】チャージドメイン2次IIR−LPFの周波数特性におけるゲインを向上させることが可能なフィルタ回路を提供する。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタと、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタと、を備え、フライングキャパシタは、入力端から出力端へ切り替わる場合には容量が小さくなり、出力端から入力端へ切り替わる場合には容量が大きくなる可変容量素子を含む、フィルタ回路が提供される。

(もっと読む)

信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法

【課題】信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法を提供すること。

【解決手段】静電容量が可変である可変キャパシタと、前記入力信号を前記可変キャパシタにサンプリングさせるサンプリングモードと、前記入力信号をサンプリングして得られた電荷を前記可変キャパシタに保持させる保持モードと、前記可変キャパシタに保持されている電荷を出力させる出力モードと、を含む回路モードを切り替えるスイッチング部とを備え、前記可変キャパシタは、前記サンプリングモード時に前記入力信号が入力される入力端子と、前記入力端子との間に絶縁層が設けられており、前記出力モード時に前記可変キャパシタの静電容量を前記サンプリングモード時の静電容量より減少させる第1の制御信号が入力され、前記保持モード時に所定の基準電圧を有する第2の制御信号が入力される制御端子と、を備える信号処理装置。

(もっと読む)

スイッチトキャパシタアンプ回路

【課題】高精度、かつ高速性および経済性に優れたスイッチトキャパシタアンプ回路を提供する。

【解決手段】スイッチトキャパシタアンプ回路1に、オペアンプ10と、オペアンプ10に入力される入力電圧をサンプリングする入力サンプリングキャパシタ21と、オペアンプ10に並列に設けられオペアンプ10から出力される電圧をサンプリングする出力サンプリングキャパシタ22と、第一スイッチ31、第二スイッチ32、第三スイッチ33、第四スイッチ34、第五スイッチ35、第六スイッチ36、第七スイッチ37からなるスイッチ群とを具備し、これらのスイッチ群の開閉によりオペアンプ10のゲイン誤差に起因して入力サンプリングキャパシタ21に残留する電荷を用いて出力電圧を補正し、出力線16に出力する。

(もっと読む)

1 - 6 / 6

[ Back to top ]