Fターム[5J032AC14]の内容

論理回路 (717) | 目的、効果 (263) | 信頼性に関するもの (237) | 電源(オフ時、断時を含む) (23) | 電源投入時 (14)

Fターム[5J032AC14]に分類される特許

1 - 14 / 14

電子回路

【課題】 リセットに起因するディジタル回路の初期化時の誤動作の発生を減らす。

【解決手段】 電子回路において、ノイズ除去回路13は、パワーオンリセット信号などのリセット信号のノイズ除去を行い、ディジタル回路11は、ノイズ除去回路13によるノイズ除去後の信号でリセットされる。そして、早期有効化回路16は、そのリセット信号によるリセット状態が解除されるまでの期間、ディジタル回路11の出力信号を所定の値に固定する。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

半導体集積回路装置

【課題】電源投入手順によらずに安定した動作を行う入出力回路の制御を、回路規模の増大を抑え、チューニングが不要なデジタル回路のみで実現する集積回路を提供する。

【解決手段】信号発生器113で生成した信号を、レベルシフト回路111で電源電圧Vcc2の信号振幅へ変換する。次にVcc2の信号振幅に変換したものを、もう一度レベルシフト回路112で内部電源電圧Vcc1の信号振幅へ変換して、フィードバック信号を生成する。比較器114で信号発生器113が生成したオリジナルの信号と、2つのレベルシフトを経て生成された、フィードバック信号とを論理的に比較し、一致しない場合にはVcc2の電源が遮断されていると見なして、入出力回路115での不定伝播を防止するように制御を行う。

(もっと読む)

CMOSバイアス回路

【課題】電源電圧の変動の影響を低減することが可能なCMOSバイアス回路を提供する。

【解決手段】CMOSバイアス回路は、起動回路と、被起動回路部と、を備え、起動電流供給部は、第1の端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され第1の電流を出力する第1の電流供給回路と、を含み、起動電流停止制御部は、内部電流をカレントミラーした停止制御電流を第1のMOSトランジスタの他端に供給し、被起動回路部は、内部電流が第1の電流値以上のときは内部電流を第2の電流値まで増加させ、起動電流が零ならば内部電流を第2の電流値で安定させ、零より大きい起動電流に応じて内部電流を第1の電流値以上に増加させる。

(もっと読む)

電子装置

【課題】本発明は、電源電圧の変動時における回路素子間の信号電圧を適切な範囲に抑制する電子装置に関する。

【解決手段】電子装置1は、信号出力回路部2が電源電圧Vaによって動作して信号を信号線5を通して信号入力回路部3に出力し、信号入力回路部3が電源電圧Vbによって動作して信号の処理を行う。保護回路部4は、信号線5に接続され、電源オフ時等において、信号線5を流れる信号の電圧値が、ダイオードD1と抵抗1との接続点Pの電位とダイオードD1の順方向電圧を加算した閾値電圧を超える電圧値になると、ダイオードD1に信号線5から電流を流して、信号線5を流れる信号の電圧値を該閾値電圧以下に抑制する。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

プルダウン回路を備える半導体装置

【課題】 面積を小さくできるプルダウン回路を備える半導体装置を提供する。

【解決手段】 エンハンスメント型(E型)NMOSトランジスタ11のオーバードライブ電圧が低くなり、その分、E型NMOSトランジスタ11はドライブ能力が高く回路設計され、E型NMOSトランジスタ11のL長が短くなるので、プルダウン回路10のデプレッション型(D型)NMOSトランジスタ12とE型NMOSトランジスタ11との合計面積の方が従来のD型NMOSトランジスタ41だけのプルダウン回路40の面積よりも小さくなる。よって、その分、半導体装置の面積も小さくなる。

(もっと読む)

レベルシフタ回路

【課題】電源投入時に出力信号値が不定にならないレベルシフタ回路を提供する。

【解決手段】信号変換回路110は、ハイレベル(VDDCORE)およびローレベル(GND)からなる信号Sinを入力し、ハイレベル(VDDIO)およびローレベル(GND)からなる信号Soutに変換して出力する。基準電圧生成回路120は、VDDCOREよりも低く且つVDDIOよりも高い基準電圧Vfを、VDDIOとGNDとの電位差を分圧することによって生成する。電圧比較回路130は、VDDCOREが基準電圧Vfよりも低いときはスイッチトランジスタ116をオンさせ且つVDDCOREが基準電圧Vfに達するとスイッチトランジスタ116をオフさせるための制御信号FIXOUTを生成する。電源投入時、VDDCOREが基準電圧Vfに達するまでは、レベルシフタ回路100の出力端子が接地され、出力信号Soutがローレベルに固定される。

(もっと読む)

論理レベル出力集積回路

【課題】ワイヤード接続されたとしても安定した論理レベルを出力端子から出力できるようにする。

【解決手段】抵抗R4およびR5が、出力回路13(A)のトランジスタM2のドレイン−ソース間と、出力回路13(B)のトランジスタM3のドレイン−ソースを通じて流れる電流の通電経路に直列に接続して構成されている。抵抗R4およびR5の抵抗値が、出力回路13(A)のトランジスタM2がオンしている間において出力回路13(B)のトランジスタM3がオンしたときのオン抵抗値よりも1桁〜2桁高い値に設定されている。

(もっと読む)

半導体回路

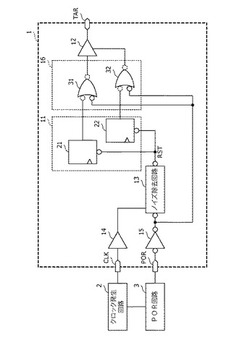

【課題】電源立ち上がり時には即座に入力信号を反映した出力を行ない、電源立ち上がり後の定常状態では従来通りの遅延処理を行うことでノイズのフィルタ機能と信号の遅延機能を実現する半導体回路を提供する。

【解決手段】コンデンサを含み、入力信号に応じて前記コンデンサを充電および放電することで前記入力信号の伝達を遅延させる遅延回路と、前記遅延回路における前記コンデンサを充電する時間より短い時間で前記コンデンサを充電する充電手段と、パワーオンリセット回路と、論理ゲートとを備えている。前期パワーオンリセット回路は、電源の立ち上がり時から一定期間パルス状の信号を出力する。また、前記論理ゲートは前記パワーオンリセット回路の出力と前記入力信号との論理演算を行ない、その出力により前記電源の立ち上がり時から一定期間のみ前記入力信号に応じて前記充電手段を動作させる。

(もっと読む)

半導体集積回路装置

【課題】電源制御後に電源に対する所望の基板電圧へ制御しようとする際、所望の基板電圧に移行するまでの移行時間が長くなるという課題があった。また電源制御、基板制御を各々の電圧に関係なく実施しようとすると、ラッチアップや耐圧劣化が発生する。

【解決手段】トランジスタ5,6で構成される被制御回路4に対し供給する電源電圧を制御する電源制御回路2と、トランジスタ5,6の基板を制御する基板制御回路1と、電源遷移中の基板を別系統から制御する特殊基板制御回路3とを設け、電源遷移中に特殊基板制御回路3により積極的に基板制御を実施し、早めに所望の基板電圧へ制御することにより、所望の基板電圧に移行するまでの時間を短縮する。また、電源電圧と基板電圧との間の電位差条件によって発生するラッチアップ、耐圧劣化の課題に対しては、電位差条件に対応した特殊基板制御回路3による電圧供給、電流供給を実施する。

(もっと読む)

パワーオンリセット回路

【課題】電源電圧の変動や電源再投入時に、誤動作を生じないパワーオンリセット回路を提供する。

【解決手段】電源投入時、リセット信号PORは“L”であるので、ノードN1の電圧V1は、抵抗11とキャパシタ13による積分回路で遅延して上昇する。これにより、リセット信号PORは遅延して“H”となり、この間にLSI内部の論理回路が初期状態に設定される。リセット信号PORが“H”になると、PMOS12,18によってノードN1とインバータ17は電源VDDから切り離される。一方、キャパシタ13はNMOS16によって放電され、ノードN2はNMOS19で接地電位GNDに保持される。従って、電源電圧VDDが変動してもリセット信号PORが“L”になることはない。また、電源が一旦遮断したときには、再投入によって確実にリセット信号PORが出力される。

(もっと読む)

電子機器及び電子機器の再起動方法

【課題】部品や回路ブロックに動作異常が発生しても、複雑な外部処理を必要とすることなく、可能な限り復旧を試み、復旧不能の場合でもリセットを際限なく繰り返さないようにし得る電子機器を提供する。

【解決手段】プログラマブルデバイスによりリセットカウンタ回路を形成し、電源オフから電源オンとなった時にシステムリセットの回数値を自動的に初期値にセットするFPGA15を用い、LANインタフェース部11及び音声ビデオCODEC16といった信号処理部単位でデバイスリセットを実行し、一定回数のデバイスリセットを繰り返した後にシステムリセットを行い、FPGA15に保持されるシステムリセットの回数値がリセット設定回数値に達した場合には、システムの起動停止もしくは電源オフを行うようにしている。

(もっと読む)

半導体集積回路装置

【課題】動作信頼性を向上出来る半導体集積回路装置を提供すること。

【解決手段】第1電源V1と、前記第1電源V1と異なる電圧の第2電源V2とを用いて動作する半導体集積回路装置1であって、前記第1電源V1が所定の電圧を超えたことを検知する第1検知回路10と、前記第2電源V2が所定の電圧を超えたことを検知する第2検知回路11と、前記第1電源V1を用いてアナログ動作するアナログ回路30の動作状況をチェックし、正常に動作しているか否かを示す制御信号CHECKを出力するチェック回路20とを具備し、前記第1検知回路10の検知レベルは前記制御信号CHECKに基づいて決定され、前記第1、第2検知回路10、11における検知結果に応じてパワーオンリセット信号POR1が出力される

(もっと読む)

1 - 14 / 14

[ Back to top ]