Fターム[5J039AC13]の内容

Fターム[5J039AC13]の下位に属するFターム

PLL(位相ロックループ) (23)

Fターム[5J039AC13]に分類される特許

1 - 8 / 8

周波数変換回路

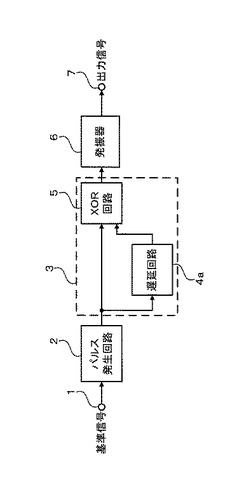

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

位相クロック発生器

【課題】より少ない数のトランジスターを使いながらも、高周波特性が反映されたクロック信号を生成でき、具現可能なクロック周波数帯域に限界がない位相クロック発生器を提供することと、回路サイズ及び電力消費量を最小化して、半導体設計及び工程が容易になり、トランジスターの動作周波数がそのまま反映された高周波クロック信号を生成することができ、ノイズ成分の影響を最小化することができる位相クロック発生器を提供する。

【解決手段】電源線及び接地線の間に繋がって4行とN列を構成して、多数の位相遅延信号をゲート端子を通じて入力されるトランジスターを含み、単位列を構成する4個のトランジスターの中で、一方の側の2個のトランジスターはNMOSでペアを構成し、他方の側の2個のトランジスターはPMOSでペアを構成して、前記単位列を構成するNMOSペアとPMOSペアの間のラインに繋がってクロック信号を送り出すバッファーを含む。

(もっと読む)

周波数逓倍装置

【課題】出力信号の精度を維持することが可能な高精度の周波数逓倍装置を低コストに提供する。

【解決手段】基準信号PREFの1周期分の時間内に生成された出力クロックRCKをカウント(計時)し、そのカウント値を表すデジタルデータDL1〜DL12をラッチ(確定)し、そのデジタルデータをクリアする、という動作を基準信号PREFの2周期毎に繰り返す結果、基準信号PREFの2周期毎にラッチされたデジタルデータDL1〜DL12である周波数制御データCD1〜CD12が新たに生成される。この新たに生成される周波数制御データ[2]は、基準信号PREFの2周期前に生成された周波数制御データ[1]を補正したものといえる。そのため、出力クロックRCKのカウント値が周波数制御データに反映され、新たな周波数制御データ[2]が生成されるまでに要する時間である補正遅延時間tは基準信号PREFの2周期分の時間になる。

(もっと読む)

高速パルスの生成装置及び高速パルスの生成方法

【課題】局部発振器を介して出力された比較的低い周波数のパルスを用い、比較的安価に高速パルスを生成できるとともに、任意の数のパルス数を有するパルス列を生成できる高速パルスの生成装置を提供することを目的とする。

【解決手段】S103で、局部発振器から出力されるパルス列を逓倍する第一の逓倍数を設定し、S104で、駆動量の指令値を第一の逓倍数で除算して整数解と余数を算出し、S107、S112で、整数解のパルス数を有するパルス列を出力すると共に、余数のパルス数を有するパルス列を出力し、S108、S113で、整数解のパルス数を有するパルス列を第一の逓倍数で逓倍して第一の逓倍パルス列を生成すると共に、余数のパルス数を有するパルス列を逓倍数1で逓倍して第二の逓倍パルス列を生成し、S115で、第一の逓倍パルス列に前記第二の逓倍パルス列を加えて、出力パルス列を生成する。

(もっと読む)

集積回路

【課題】 内部回路が逓倍クロック信号に基づいて動作することによる電源変動の影響が、クロック信号出力回路に及ぶことを極力回避できる集積回路を提供する。

【解決手段】 電源配線14がデジタル回路群17を経由してクロック信号出力回路11に電源供給を行う経路中にローパスフィルタ22を配置し、電源配線14を伝搬しようとするノイズ成分をアナロググランド側に逃がして除去する。そして、クロック信号出力回路11による逓倍クロック信号fmの発振精度を向上させ、その逓倍クロック信号fmに同期して動作するデジタル回路群17における通信ブロック16の通信精度等を向上させる。

(もっと読む)

クロック信号出力回路

【課題】 電源電圧が変動する場合でも、逓倍クロック信号の出力精度を極力維持することができるクロック信号出力回路を提供する。

【解決手段】 周期カウンタ4では、基準クロック信号fsの周期をリングオシレータ1より出力される高速クロック信号frでカウントし、周期カウンタ24ではN分周された基準クロック信号fsの周期をN分周した高速クロック信号frでカウントする。そして、有効判定回路25は、周波数逓倍動作を開始した直後はマルチプレクサ26により周期カウンタ4側の周期データD1を選択して逓倍クロック信号fmを迅速に出力し、それ以降、周期カウンタ24によってカウントされた周期データD1’が有効になる時間が経過すると、当該周期データD1’を選択するようにマルチプレクサ26を切替えて周波数逓倍演算処理の対象とする。

(もっと読む)

1 - 8 / 8

[ Back to top ]