Fターム[5J039FF04]の内容

パルスの操作 (9,993) | パルス特性(個々のパルス) (109) | ピーク位置 (10)

Fターム[5J039FF04]の下位に属するFターム

微分して零クロス点を検出するもの (2)

レベル判別手段を持つもの (2)

差分方式によるもの (1)

Fターム[5J039FF04]に分類される特許

1 - 5 / 5

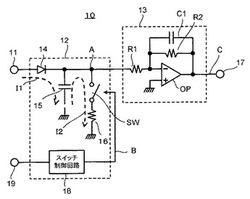

ピークホールド形検波回路

【課題】RPIが大きく変動しても出力電圧の変動が少ない、ピークホールド形検波回路を提供すること。

【解決手段】本発明の一例のピークホールド形検波回路によれば、検波される高周波パルスが入力される入力端子にアノード端子を接続された検波ダイオードと、この検波ダイオードのカソード端子と接地間に接続されたキャパシタと、前記検波ダイオードのカソード端子に一端を接続されたスイッチ回路と、このスイッチ回路の他端と接地間に接続された放電用抵抗と、前記検波ダイオードのカソード端子に入力端子を接続され入力信号を積分する積分器と、前記高周波パルスに同期してこの高周波パルスよりも幅の広い制御用高周波パルスを前記スイッチ回路に制御信号として入力するスイッチ制御回路と、を有する。

(もっと読む)

ピークレベル検出装置

【課題】1ビットオーディオ信号のピーク値を求めることを、低演算量かつ高精度で実現可能な装置を提供すること。

【解決手段】1ビットストリームが供給されるとディレイバッファ30に順次データが書き込み記憶される。そして、ピーク位置検出部10が、ディレイバッファ30に記憶されたピーク値のアドレスである最大ピークアドレスを検出しこれをデータ読み出し部20に送る。データ読み出し部20は、送られてきた検出された最大ピークアドレスに応じてディレイバッファ30の対応するデータを読み出す。そして、LPF40は、この読み出されたデータの低域を通過させ、最後にABS部50が信号を絶対値化してマルチビットピーク値を出力する。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

信号増幅装置

【課題】安価な標準CMOSを用いて、高精度にしきい値設定制御を行う。

【解決手段】オフセット電圧発生部11は、入力信号の直流レベルを検出し、正側オフセット電圧信号を生成して出力、あるいは、負側オフセット電圧信号を生成して出力する。ピーク検出部21は、正側オフセット電圧信号のレベルが入力信号の最大レベルよりも大きい場合は、正側オフセット電圧信号を出力し、入力信号の最大レベルが正側オフセット電圧信号よりも大きい場合は、入力信号の最大レベルをピーク値として出力する。ボトム検出部22は、負側オフセット電圧信号のレベルが入力信号の最小レベルよりも小さい場合は、負側オフセット電圧信号を出力し、入力信号の最小レベルが負側オフセット電圧信号よりも小さい場合は、入力信号の最小レベルをボトム値として出力する。分圧部23は、ピーク値とボトム値とを分圧して、しきい値レベルを発生する。

(もっと読む)

ピーク検出回路

【課題】出力信号の低下を抑えることが可能なピーク検出回路を提供することを目的とする。

【解決手段】NチャネルのMOSFET2に並列接続されるPチャネルのMOSFET4のソース端子と電源電圧VDDが印加される端子10との間に抵抗6を接続し、NチャネルのMOSFET3に並列接続されるPチャネルのMOSFET5のソース端子と電源電圧VDDが印加される端子10との間に抵抗7を接続し、MOSFET2、5のそれぞれのゲート端子に入力信号INPを入力し、MOSFET3、4のそれぞれのゲート端子に入力信号INPの反転信号INNを入力する。

(もっと読む)

1 - 5 / 5

[ Back to top ]