Fターム[5J039KK08]の内容

Fターム[5J039KK08]に分類される特許

1 - 5 / 5

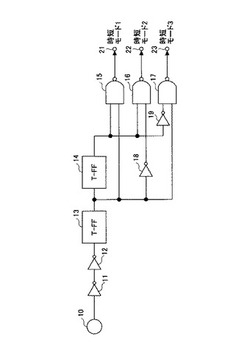

モード設定回路及びそれを用いたカウンタ回路

【課題】本発明は多種の時短モード設定が可能なモード設定回路及びそれを用いたカウンタ回路を提供することを目的とする。

【解決手段】外部から供給されるパルス信号によりトリガされる縦続接続された複数段のフリップフロップ13,14と、複数段のフリップフロップそれぞれの出力信号を演算して複数種類のモード信号を生成する論理回路15〜19とを有する。

(もっと読む)

クロック制御回路およびそれを搭載した半導体集積装置

【課題】ダブルエッジトリガ型フリップフロップ回路に対するクロック信号の供給を停止させるとき、当該フリップフロップ回路が保持するデータが不必要に更新されてしまうことがある。

【解決手段】エッジ検出回路61は、第1クロック信号を受け、そのエッジを検出すると、所定幅のパルス信号を出力する。論理ゲートは、エッジ検出回路61の出力信号と、ダブルエッジトリガ型フリップフロップ回路の使用状態を示すイネーブル信号とを受け、イネーブル信号が有意な期間、エッジ検出回路61の出力信号に追従する信号を出力し、イネーブル信号が非有意な期間、非有意なレベルの信号を出力する。トグル型フリップフロップ回路は、論理ゲートの出力信号を受け、所定幅のパルス信号を検出するたびに、論理レベルが反転する信号を、第2クロック信号として出力する。

(もっと読む)

デジタルフィルタ装置、位相検出装置、位置検出装置、AD変換装置、ゼロクロス検出装置及びデジタルフィルタ用プログラム。

【課題】ゼロクロスする信号からチャタリング等のノイズの影響を除去可能なデジタルフィルタ装置を提供する。

【解決手段】2値のデジタル信号DINをフィルタリングして2値のデジタル信号DOUTを出力するデジタルフィルタ装置4は、トリガ信号が入力される度に、デジタル信号DOUTの信号レベルを切り換えるトグルフリップフロップ12と、デジタル信号DINの信号レベルと、出力デジタル信号DOUTの信号レベルとが、不一致となる間、第1イネーブル信号EN1を出力するXOR回路13と、第1イネーブル信号EN1が出力されている間、クロック信号CLKに同期して計数していき、計数値が上限値に到達したときに、計数値を初期値に戻すとともにトリガ信号としてのキャリーオン信号ON_RCOをトグルフリップフロップ12へ出力するチャージカウンタ14とを備える。

(もっと読む)

クロック供給回路、半導体システムおよびその設計方法

【課題】ゲーテッドクロック機能を有し、トランジスタの経時劣化に起因するクロックスキューを抑制できるクロック供給回路を提供する。

【解決手段】クロックゲート回路GCにおけるセレクタ31はイネーブル信号ENがハイレベルのときクロック信号を通過させ、イネーブル信号ENがローレベルのときトグルフリップフロップ21の出力信号を通過させる。トグルフリップフロップ21はイネーブル信号ENが立ち上がり遷移をするごとに記憶値を反転させて出力する。イネーブル信号ENがローレベルに変化するたびにバッファ15,16及びフリップフロップF3,F4の論理レベルはローレベル固定状態とハイレベル固定状態とに交互に切り替えられる。ハイレベル固定期間とローレベル固定期間が同じとみなせ、バッファ13,14とバッファ15,16のNBTIによる遅延劣化の影響は等しくなり、クロックスキューを抑制できる。

(もっと読む)

クロック発生回路、信号多重化回路及び光送信器、並びに、クロック発生方法

【課題】 トグルフリップフロップ回路(TFF)を用いて分周クロック信号を発生させる場合に、初期状態が定まらないというTFFの本質的な問題に起因して、発生する各分周クロック信号間に位相ずれが生じてしまうのを回避しながら、4チャンネルよりも多くのチャンネル数のデータ信号の多重化を実現できるようにする。

【解決手段】 クロック発生回路であって、位相の異なる一対の分周クロック信号を出力しうる複数のトグルフリップフロップ回路TFF1,TFF2を直列に接続し、トグルフリップフロップ回路TFF2から出力される一対の分周クロック信号の一方又は両方をディレイさせて一対の分周クロック信号とは異なる位相のクロック信号として出力しうるディレイ回路DFF1を、トグルフリップフロップ回路TFF2に接続して構成される。

(もっと読む)

1 - 5 / 5

[ Back to top ]