Fターム[5J039MM12]の内容

Fターム[5J039MM12]に分類される特許

1 - 8 / 8

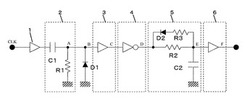

発振停止検出回路

【課題】保護継電器や監視制御機器の発振回路が停止したときに、発振停止検出回路を安価に構築する。

【解決手段】本発明の発振停止検出回路は、発振回路がクロックの供給の停止を検出するために、クロック信号の変化を検出する微分回路と、微分回路からの信号を立ち上がりに限定するダイオードと、前記出力信号を整形する、パルス整形回路とインバータ回路と、充放電回路と、充放電回路の出力電圧レベルと所定の基準値を比較して、基準値を超えたときに信号出力をすることを特徴とする。

(もっと読む)

位相比較装置

【課題】高速動作するBang-Bang型位相比較回路の出力パルスに歪や欠損がある場合であっても、チャージポンプやA/D変換器を用いることなく、進相、遅相のいずれであるかを正確に表すデジタル信号を得る。

【解決手段】Bang-Bang型の位相比較回路10と、該位相比較回路の進相出力パルスおよび遅相出力パルスを入力して遅相/進相の識別を行う位相比較結果識別回路20とを備える。位相比較結果識別回路20は、位相比較回路10の進相出力パルスによってリセットされた後にクロック信号のカウントを行い所定のカウント値に達すると遅相を示す信号を出力する第1カウンタ回路21と、位相比較回路10の遅相出力パルスによってリセットされた後に前記クロック信号のカウントを行い所定のカウント値に達すると進相を示す信号を出力する第2カウンタ回路22と、前記遅相を示す信号と前記進相を示す信号を入力して進相/遅相の識別信号を出力する識別回路23とを具備する。

(もっと読む)

位相クロック発生器

【課題】より少ない数のトランジスターを使いながらも、高周波特性が反映されたクロック信号を生成でき、具現可能なクロック周波数帯域に限界がない位相クロック発生器を提供することと、回路サイズ及び電力消費量を最小化して、半導体設計及び工程が容易になり、トランジスターの動作周波数がそのまま反映された高周波クロック信号を生成することができ、ノイズ成分の影響を最小化することができる位相クロック発生器を提供する。

【解決手段】電源線及び接地線の間に繋がって4行とN列を構成して、多数の位相遅延信号をゲート端子を通じて入力されるトランジスターを含み、単位列を構成する4個のトランジスターの中で、一方の側の2個のトランジスターはNMOSでペアを構成し、他方の側の2個のトランジスターはPMOSでペアを構成して、前記単位列を構成するNMOSペアとPMOSペアの間のラインに繋がってクロック信号を送り出すバッファーを含む。

(もっと読む)

信号伝達回路

【課題】入力側と出力側とを電気的に絶縁状態にするトランスの結合係数が悪くても誤動作することがない信号伝達回路を提供することを目的とする。

【解決手段】入力信号の立上りタイミング及び立下りタイミングにおいて、それぞれ、パルス電圧を発生させる1次側回路111と、1次側回路111で発生されるパルス電圧を1次側コイルで受けるトランス113と、トランス113の2次側コイルに発生するパルス電圧のうち、最初のパルス電圧の発生タイミングで出力信号を立ち上がらせ、次に発生するパルス電圧の発生タイミングで出力信号を立ち下がらせる2次側回路2とを備えて信号伝達回路1を構成し、最初のパルス電圧が発生してから所定時間、または、次のパルス電圧が発生してから所定時間、2次側コイルに発生するパルス電圧が無視されるように2次側回路2を構成する。

(もっと読む)

異常検出回路

【課題】発振回路の停止検出などを行う異常検出回路を半導体集積回路で形成する場合に、抵抗素子や容量素子を半導体集積回路内に作成する必要がない上に、外付け部品として用意する必要がない異常検出回路の提供。

【解決手段】この発明は、発振回路の発振停止を検出するとともに、半導体集積回路内に形成される異常検出回路であって、容量素子C1と抵抗素子R1で構成される積分回路123を含んでいる。容量素子C1は、半導体集積回路の未使用のボンディングパッド24aに寄生する寄生容量を使用するようにした。抵抗素子R1は、MOSトランジスタを使用して、そのオン抵抗を利用するようにした。

(もっと読む)

クロック信号停止判定回路

【課題】クロック信号の立ち上がりエッジを検出するようにして、波形の悪いクロック信号の停止判定を行うことができるようした。

【解決手段】エッジ検出回路11は、排他的論理和11aと、コンデンサと抵抗からなる遅れ回路11bから構成される。このエッジ検出回路11の入力端にクロック信号12が入力されると、エッジ検出回路11は、入力されるクロック信号を排他的論理和11aと遅れ回路11bにより、出力には幅の狭いパルス信号13を送出する。

この幅の狭いパルス信号13は、LPF14に入力されて処理されると、LPF14の出力には、図示波形の信号15を得る。この波形の信号15は、ウィンドウコンパレータ16で異常判定レベルH,Lと比較判定される。判定結果がウィンドウコンパレータ16から出力される。

(もっと読む)

信号分析装置

【課題】欠損が発生した場合の影響を、従来方式よりも低減することができる信号分析装置を得る。

【解決手段】到来時間間隔と継続時間との差である相違パラメータを所定範囲内で複数個設定する相違パラメータ設定部10と、継続時間と相違パラメータとを加算して複数の到来時間間隔を算出する到来時間間隔算出部20と、予め定められた到来時間間隔の細分区間に基づいて、複数の到来時間間隔のそれぞれを該当する細分区間に区分する細分区間選出部30と、それぞれの細分区間に区分された到来時間間隔に対して、到来時間および到来時間間隔に基づく複素数を算出して区分ごとの合計値を算出する位相累積算出部40と、それぞれの細分区間ごとの合計値に基づいて、周期的な放射信号の有無および周期的な放射信号の到来時間間隔を特定する周期性判定部50とを備える。

(もっと読む)

発振検知回路

【課題】トランジスタ特性のバラツキに影響されることなく、発振回路の発振を安定的に検知することが可能な発振検知回路を提供すること。

【解決手段】電源VDDとグランドVSSとの間に電流源IS11,IS12が直列に接続される。電流源IS11と電流源IS12との接続点P1にはコンデンサC1が接続され、この接続点P1に現れる信号を積分する。電流値の大きな電流源IS11と接続点P1との間にはスイッチSW1が設けられる。シュミットトリガーST1は、積分された信号を入力して2値信号を出力する。この2値信号は論理積回路ANに入力され、検知信号OSCSTPが出力される。ここで、発振回路の出力信号NCKMに基づきスイッチSW1が開閉すると、電流I11が断続的にコンデンサC1に供給される。この結果、接続点P1の信号レベルが上昇し、検知信号OSCSTPがハイレベルとなって発振が検知される。

(もっと読む)

1 - 8 / 8

[ Back to top ]