Fターム[5J055DX88]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 複数の素子で構成される主スイッチ (1,328) | 同様の構成の繰り返しが部分的にあるもの (12)

Fターム[5J055DX88]に分類される特許

1 - 12 / 12

半導体装置

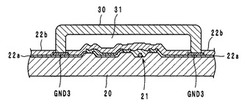

【課題】スイッチ回路部で生じる高周波輻射が論理回路部へ悪影響を及ぼすことを抑制でき、かつ、小型化、低コスト化を犠牲にすることのない半導体装置を得る。

【解決手段】スイッチ回路部を論理回路部にてスイッチング動作させる半導体装置(アンテナスイッチ)。スイッチ回路部と論理回路部とが単一の半導体基板20上に形成されており、論理回路部の直上にシールド導体30が配置されている。シールド導体30はエアブリッジ構造とされ、グランド端子GND3に接続されている。

(もっと読む)

高周波信号用スイッチ回路

【課題】高周波信号の歪が少ない高周波信号用スイッチ回路を提供する。

【解決手段】SOI基板上に形成された高周波信号用スイッチ回路において、1つのアンテナ端子ANTと複数の高周波端子との間にそれぞれスルースイッチ部を設ける。スルースイッチ部M4Tにおいては、アンテナ端子ANTと高周波端子RF4との間にn個(nは2以上の整数)の電界効果型トランジスタM1〜Mnを直列に接続する。トランジスタM1〜Mnは、共通の制御信号Cont4に基づいてオン状態とオフ状態とを切替える。また、スルースイッチ部M4Tには電界効果型トランジスタMxを設け、トランジスタMnに対して並列に接続する。トランジスタMxのゲートには常時電源電位Vddを印加し、常時オン状態とする。

(もっと読む)

半導体集積回路装置および高周波電力増幅モジュール

【課題】アンテナスイッチの各トランジスタに流れる高周波電流の変化量を低く抑え、高調波歪みを大幅に低減する。

【解決手段】SP6Tスイッチのシャント部31(,32)は、FETなどからなるトランジスタ53〜56、抵抗57〜66、およびDCカット容量となる静電容量素子67〜69から構成されており、抵抗61〜65の抵抗比は、たとえば、1:2:2:2:1となるように設定されている。このように、抵抗比を1:2:2:2:1として抵抗分割することによって、オフ時の基本スイッチを構成する多段に接続されたトランジスタ53〜56にかかるゲート−ソース間電圧、ゲート−ドレイン間電圧、ドレイン・ソース間電圧を均等化でき、特定のトランジスタのゲート−ソース間容量、およびゲート−ドレイン間容量に流れる高周波電流変化が大きくなることを防ぎ、歪を低く抑えることができる。

(もっと読む)

負荷駆動装置

【課題】ハイサイド,ロウサイドの駆動用トランジスタを備える場合、タイマ等の回路を付加することなく双方のトランジスタの熱的負担を均等化する負荷駆動装置を提供する。

【解決手段】ハイサイドのFET4を発熱源として、ロウサイド電流制御部を構成する抵抗素子6と、トランジスタTr3,Tr4とに対して付与される温度勾配が異なるように各素子を配置して、ロウサイド電流制御部がFETをフルオン制御した後に定電流制御に、ハイサイド電流制御部がFET4を定電流制御した後にフルオン制御に移行させる。具体的には、FET4の形成領域に対してロウサイド電流制御回路の抵抗素子6を近接側に配置し、カレントミラー回路を構成するトランジスタTr3,Tr4を上記形成領域の遠隔側に配置する。

(もっと読む)

負荷駆動回路

【課題】負荷に対する電力供給の駆動動作が駆動信号に追従するとともに、電源電圧の低下に対応することができる負荷駆動回路を提供する。

【解決手段】負荷駆動回路は、電流制限抵抗を介して負荷に接続されるとともに、定電圧電源に接続される第1の駆動回路と、第1の駆動回路と並列に負荷に接続されるとともに、定電圧電源に接続される第2の駆動回路と、電流制限抵抗の電流値を検出する抵抗電流値検出回路と、駆動信号が入力されると第1の駆動回路を制御して負荷に対して定電圧電源から電力を供給し、定電圧電源の電圧を検出して電圧が所定の値を下回り、抵抗電流値検出回路において検出される電流値が所定の値を超えないとき、第2の駆動回路を制御して負荷に対して定電圧電源から電力を供給する制御部とを有する。

(もっと読む)

高周波スイッチ回路

【課題】チップサイズを増大することなく相互変調歪及び高調波歪が低減可能な高周波スイッチ回路を提供する。

【解決手段】アンテナ端子と、第1及び第2のRF端子と、前記アンテナ端子と前記第1のRF端子との間に配置された第1のスルートランジスタと、前記アンテナ端子と前記第2のRF端子との間に配置された第2のスルートランジスタと、接地と前記第1のRF端子との間に配置された第1のシャントトランジスタと、接地と前記第2のRF端子との間に配置された第2のシャントトランジスタと、互いに逆方向となるように並列接続されたMOSキャパシタを有し、前記アンテナ端子と前記接地との間、及び前記第1及び第2のRF端子のいずれかと前記接地との間、の少なくともいずれかに配置された歪補償回路と、を備え、前記アンテナ端子と、前記第1及び第2のRF端子と、の間の電気的接続が切り替え可能とされたことを特徴とする高周波スイッチ回路が提供される。

(もっと読む)

電力供給制御装置

【課題】複数の半導体スイッチ素子を並列接続して負荷への電力供給制御を行う場合に、部品点数を軽減しつつ半導体スイッチ素子間のばらつきによる異常電流判定のばらつきを抑制することが可能な電力供給制御装置を提供する。

【解決手段】電源61(車両用電源)と負荷50との間の通電路63に並列接続された2つの半導体スイッチ装置11a,11bは、それぞれから出力されるセンス電流Is1、Is2の合成センス電流Isを共通のRC並列回路12に流し、各半導体スイッチ装置11a,11bは、そのRC並列回路12の端子電圧Voを閾値電圧としての分圧電圧Vrと比較して電流異常を検出する。

(もっと読む)

出力回路

【課題】入力信号に応じた信号を出力端子から出力する出力回路に関し、複数の信号が衝突した場合であっても出力信号を安定化できる出力回路を提供することを目的とする。

【解決手段】本発明は、入力信号に応じた信号を出力端子から出力する出力回路において、入力信号を増幅する第1の増幅回路(112)と、入力信号を増幅する第2の増幅回路(113)と、第1の増幅回路(112)の出力信号に応じてスイッチングされ、オン時に出力端子(Tout0)に電流を供給する第1のトランジスタ(114)と、第2の増幅回路(113)の出力信号に応じてスイッチングされ、オン時に出力端子(Tout0)から電流を引き込む第2のトランジスタ(115)と、入力信号に応じて第1の増幅回路(112)の動作を制御する第1の制御回路(116)と、入力信号に応じて第2の増幅回路(113)の動作を制御する第2の制御回路(117)とを有することを特徴とする。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】半導体スイッチング素子の駆動回路において、アーム短絡防止回路の駆動ばらつきを抑制するとともに、外部ノイズによる誤動作を防止する。

【解決手段】直流電源の出力端子間に直列接続した第1および第2の半導体スイッチング素子のゲートとエミッタ間にスイッチを接続し、

上記素子に制御信号を入力することにより、オン/オフ駆動する駆動回路が、上記の制御信号とゲート入力信号がともにオフ状態にあることを検出して、上記素子のゲートとエミッタ間を、スイッチを用いて短絡させる検出器を有することを特徴とし、

上記の検出器が論理回路で構成され、制御信号とゲート入力信号がともにオフ状態から、ゲート入力信号のみがオン状態に移行する遷移モードを検出しないものとし、上記遷移モードでは、上記素子のゲートとエミッタ間の短絡が継続して行われることを特徴とする。

(もっと読む)

高周波スイッチ回路及び半導体装置

【課題】小型かつ高性能の高周波スイッチ回路を提供する。

【解決手段】入出力端子161及び162と接地端子181及び182との間、及び入出力端子161〜163の間に、直列接続された複数のFET111〜118及び121〜128によって構成されたスイッチ部をそれぞれ設ける。また、一方の端子が各FET111〜118及び121〜128のゲート電極に接続され、他方の端子にスイッチ部をオン状態とオフ状態とに切り替える制御電圧171及び172が印加される複数のゲートバイアス抵抗131〜138、141〜148を設ける。各スイッチ部に含まれるFETのうち、スイッチ部がオフ状態であるときに信号電力が印加される側のFET114、115、124及び125については、ゲート電極に接続されるゲートバイアス抵抗134、135、144及び145の抵抗値を最も大きくする。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】効率的な遅延回路を実現することができる汎用ロジックセル、それを用いた半導体装置、及びその半導体装置の製造方法を提供すること

【解決手段】半導体装置70Aは、複数の汎用ロジックセル60´と、それら複数の汎用ロジックセル60´に接続された電源線11と、それら複数の汎用ロジックセル60´に接続された接地線12と、第1配線81Aと、第2配線82Aとを備える。この時、第1配線81Aは、ある汎用ロジックセル60´の第3のノード3と、第4のノード4と、第5のノード5とを接続する。また、第2配線82Aは、電源線11と、その汎用ロジックセル60´の第1のノード1とを接続する。

(もっと読む)

高周波スイッチ回路装置

【課題】 アイソレーション確保用のシャントFETを有する場合でも、シャントFET用の制御信号入力端子を増加させずに駆動し、しかもチップサイズを小型化する。

【解決手段】 ショットキー接合よりなるダイオードD1〜D6を用い、制御信号入力端子CTL1〜CTL3の電圧の高い方を選択することのできるダイオードロジック回路OR1をスイッチ用およびアイソレーション確保用のMESFET段FET1〜FET6を形成した化合物半導体基板に一体的に形成する。そして、複数の制御電圧入力端子CTL1〜CTL3の電圧でスイッチ用のMESFET段FET1〜FET3を制御し、ダイオードロジック回路から出力されるOR電圧によりアイソレーション確保用のMESFET段FET4〜FET6を制御する。さらに、このダイオードロジック回路OR1をFETの中間接続点に接続することで、電源端子を追加せずに、FETの中間接続点の電位を固定する。

(もっと読む)

1 - 12 / 12

[ Back to top ]