Fターム[5J055EX28]の内容

Fターム[5J055EX28]の下位に属するFターム

トランス駆動、入力絶縁 (17)

光電素子、光学的結合 (26)

Fターム[5J055EX28]に分類される特許

1 - 8 / 8

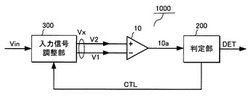

ヒシテリシス装置

【課題】簡易な構成でヒシテリシス特性を付与する。

【解決手段】ヒシテリシス装置1000は、複数の閾値に対応するオフセット電圧を入力信号Vinに付加した調整信号Vxを出力する入力信号調整部300と、調整信号Vxに基づいて2値化した第1信号10aを出力するコンパレータ10と、入力信号調整部300を制御して複数の閾値ごとにオフセット電圧を切り替えるとともに、オフセット電圧の切り換えごとに第1信号10aを取得し、複数の閾値に対応する第1信号10aと前回の出力信号DETとに基づいて今回の出力信号DETを生成する判定部200とを備える。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

スイッチ回路

【課題】スイッチング素子のサイズを増大させることなく、逆電圧によるスイッチング素子の破損を防止できるようにする。

【解決手段】オンオフ制御信号(CS)に応じて2つの端子(T1,T2)間のオンオフ状態が切り替わるスイッチ回路において、端子(T1,T2)間に接続されたデュアルゲート型スイッチング素子(11)を有したスイッチ部(10)を設ける。また、デュアルゲート型スイッチング素子(11)のオンオフ状態を制御する制御部(20)を設ける。そして、デュアルゲート型スイッチング素子(11)のゲートをオフにすることによって該デュアルゲート型スイッチング素子(11)のドレイン・ソース間に所定以上の逆電圧(0Vを含む)が印加されることとなる場合には、オンオフ制御信号(CS)にかかわらず、制御部(20)によって、そのドレイン・ソースに対応したゲートをオンにする。

(もっと読む)

サンプル・ホールド回路及びデジタルアナログ変換回路

【課題】電荷分配を行う容量の容量値が小さくても、アンプの入力容量による出力誤差が小さい、高精度出力のサンプル・ホールド回路、シリアルDACの提供。

【解決手段】第1のスイッチ110を介して接続された第1及び第2の容量素子C11,C12と、差動回路と、を備え、前記差動回路は、差動入力対の第1入力が、前記第1の容量素子の一端N11に第2のスイッチ121を介して接続され、第2入力が、前記第2の容量素子の一端N8に接続された差動入力段と、前記差動入力段の出力を入力に受け、出力がサンプル・ホールド回路の出力端子N9に接続されるとともに、第3のスイッチ122を介して、前記差動入力段の前記第1入力に接続される増幅段16と、を備えている。

(もっと読む)

ブランキング回路

【課題】セトリングタイムの高速化を図ることができるブランキング回路を提供する。

【解決手段】2つのPチャンネルMOSFETQ1,Q3と2つのNチャンネルMOSFETQ2,Q4とをそれぞれ交互に接続し、第一のPチャンネルMOSFETと第一のNチャンネルMOSFETとの接続点、及び、第二のPチャンネルMOSFETと第二のNチャンネルMOSFETとの接続点とを電極OUTに接続し、第一のPチャンネルMOSFETと第二のNチャンネルMOSFETとがオンする場合に、第二のPチャンネルMOSFETと第一のNチャンネルMOSFETとがオフし、第一のPチャンネルMOSFETと第二のNチャンネルMOSFETとがオフした場合に、デッドタイム経過後に第二のPチャンネルMOSFETと第一のNチャンネルMOSFETとがオンして負荷容量を短絡するように構成してあることを特徴とするブランキング回路。

(もっと読む)

インターフェース回路

【課題】入力部3の入力信号S1を制御部2に入力するものにあって、入力部3と制御部2との間に接続された抵抗素子R3の発熱を防止することで、抵抗素子R3の耐久性を向上させる。

【解決手段】制御部2に接続された入力部3の入力信号S1を入力インターフェース部4を介して制御部2に入力するようにした入力インターフェース回路1において、入力部3と制御部2との間に接続された抵抗素子R1の発熱を防止すべく、入力部3からの入力信号S1を間欠的に制御部2に入力させる間欠入力手段5が設けられている。

(もっと読む)

半導体集積回路装置およびスイッチ入力回路

【課題】スイッチ入力回路を極力少ない外付け部品により構成し且つ低耐圧プロセスを採用可能とする。

【解決手段】イグニッションスイッチ3がオンすると、バッテリ2から抵抗23を通してMOSFET33に電流ID1が流れ、それに応じてMOSFET34にも電流ID2が流れる。入力端子22aの電圧Vinは、MOSFET33のゲート・ソース間電圧VGSに制限される。MOSFET34のドレイン電圧VD2がシュミットインバータ36の低レベルしきい値Vnよりも低い場合、判定信号SIGがHレベルになり、スイッチ入力回路26はイグニッションスイッチ3がオンしたことを検出する。

(もっと読む)

マルチチャネルサンプルホールド回路およびマルチチャネルA/D変換器

【課題】信号入力端子の電気的な入力条件によらず、小さいチップ面積で且つ高精度のチャネル切り替えを可能とする。

【解決手段】全チャネルが非選択の場合、制御回路4は、スイッチS1、S11、S12、S21、S22、S31、S32をオンとし、スイッチS13、S14、S23、S24、S33、S34をオフとする。Ch1を選択してホールドする場合、スイッチS1、S11、S12をオフし、続いてスイッチS13、S14をオンする。入力信号Vin1により充電されているコンデンサCS10は、電荷を保存したままオペアンプ3の入出力端子間に接続され、入力信号Vin1がホールドされて出力端子2から出力電圧Voutとして出力される。

(もっと読む)

1 - 8 / 8

[ Back to top ]