Fターム[5J055EX30]の内容

Fターム[5J055EX30]に分類される特許

1 - 20 / 26

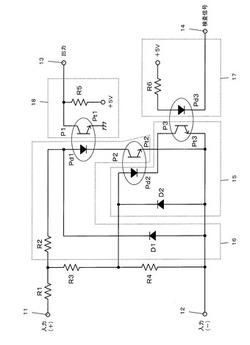

接点入力回路

【課題】閾値電圧設定回路の抵抗器の開放故障に対するフェールセーフ性を確保し、且つ、検査信号がオフ制御されたときの消費電力を低減できる接点入力回路の実現。

【解決手段】接点入力回路10は、接点の開閉状態を示す入力信号が入力される正入力端子11と負入力端子12との間に、第1抵抗器R1、第3抵抗器R3及び第4抵抗器R4が直列接続されている。そして、直列接続された第3抵抗器R3及び第4抵抗器R4に対して、第2抵抗器R2、第1フォトカプラP1のフォトダイオードPd1及び第2フォトカプラP2のフォトトランジスタPt2が順方向に直列接続されてなる第2回路部16が並列接続されている。また、第4抵抗器R4に対して、第2フォトカプラP2のフォトダイオードPd2及び第3フォトカプラP3のフォトトランジスタPt3が順方向に直列接続されてなる第1回路部15が並列接続されている。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

電子リレー

【課題】制御部及びゲート駆動部によって消費される電力を抑制しつつ、負荷の起動時に突入電流を流しきることが可能な電子リレーを提供する。

【解決手段】商用電源6と負荷7に直列接続され、トランジスタ構造を有するスイッチ素子を用いた開閉部11と、負荷の起動及び停止を制御する制御部12と、制御部12とは絶縁され、スイッチ素子のゲート電極にゲート駆動信号を出力するゲート駆動部13と、制御部12及びゲート駆動部13を動作させるための電力を確保する電源部14を備え、制御部12は、負荷7の起動時に、ゲート駆動部13に、所定時間だけスイッチ素子のゲート電極に対して、定常安定動作時よりも多くの駆動電力を供給させる。

(もっと読む)

過電流保護装置およびレーザ装置

【課題】所定の電流値以上の電流が流れることを検出すると、電源から遮断する過電流保護回路の偶発的な故障に起因して、所定の電流値以上の電流を継続して出力装置に流れるのを未然に防止することが可能な過電流保護装置を提供する。

【解決手段】この過電流保護装置5は、レーザ出力装置4に供給する電流値を監視するとともに過電流が流れた際に電流を遮断する過電流保護回路5aと、過電流保護回路5aが正常に動作するか否かを確認するトランジスタ32(TR2)、抵抗33(R4)、接点RY1−3、接点RY1−2、電源23、接点RY1−1、および、フォトカプラ34(PHC1)とを設ける。

(もっと読む)

電力変換装置のゲート制御回路

【課題】直列接続されたスイッチング素子の直流短絡事故などを防止するとともに、ゲートパルス信号用のライトガイドの本数を削減する。

【解決手段】直列接続されたスイッチング素子を駆動するゲート駆動回路と、このゲート駆動回路に与える基準信号を発生し、インターロック手段を備えたゲート信号発生手段と、このゲート信号発生手段から光伝送された信号を受光してゲート駆動回路に分配する光分配回路と、この光分配回路の出力をゲート駆動回路に夫々供給する手段と、ゲート駆動回路の出力を監視し、光分配回路にフィードバックするゲート信号監視手段と、ゲート信号監視手段のフィードバック信号が全てオフ状態であればオフ、1つでもオンであればオンとみなす論理演算手段と、論理演算手段の出力を光変換してゲート信号発生手段に供給する伝送手段とで構成する。この伝送手段の出力を、インターロック手段のインターロック条件に反映させる。

(もっと読む)

負荷制御装置

【課題】スイッチ素子の発熱を抑制して小型化を図りつつ、開閉タイミングを正確に制御して、調光制御等の高度な負荷制御を行うことができる負荷制御装置を提供する

【解決手段】操作部28に入力された操作に応じて、制御部13が交流電源の1/2周期のうちトランジスタ構造の主開閉部11を導通させるために計数される主開閉部導通時間を設定し、電圧検出部18が第3電源部16に入力される電圧が所定の閾値に達したときから計数される第1所定時間と、主開閉部導通時間とが重複している時間だけ、主開閉部11を導通させることにより調光制御する。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

半導体リレーモジュール

【課題】高周波特性を向上させるとともに、発光素子と制御素子を封止する透光性樹脂の形状を所望の形状に保持しやすい半導体リレーモジュールを提供する。

【解決手段】半導体リレーモジュールAは、ソース電極同士が接続されたMOSFET11,12からなり、高周波信号用の信号伝送線路110の途中に設けられた半導体スイッチ1と、入力信号に応じて光信号を発光する発光ダイオード31と、発光ダイオード31からの光信号を受光する受光素子を有し当該受光素子の出力に応じてMOSFET11,12のオン/オフを制御する制御IC32と、制御IC32が備える受光素子および発光ダイオード31を光学的に結合させた状態で樹脂封止する透光性樹脂8を備える。制御IC32は、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に配置され、導体パターン113とランド132との間にはLPF4が挿入される。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

駆動回路、駆動方法、固体撮像装置および電子機器

【課題】電源電圧の低電圧側の電圧と高電圧側の電圧との間の中間電圧での駆動を、トランジスタのゲート酸化膜に高耐圧素子構造を適用することなく実現できるようにする。

【解決手段】第1,第2出力バッファ回路20,30Aを用いた駆動回路10において、当該駆動回路10を構成するトランジスタのゲート酸化膜にその耐圧ΔVlimを超える電圧を印加することなく、第1出力バッファ回路20の作用によって耐圧ΔVlimを超えた電圧振幅VL−VHで駆動する。これに加えて、第2出力バッファ回路30Aにおいて、出力端子35側のトランジスタMp32,Mn32を、バイアス電圧の定常印加でなく、耐圧範囲内の電圧(VL〜VD,VS〜VH)で駆動するとともに、ノードN31,N32側のトランジスタMp31,Mn31を、耐圧範囲内の電圧でなく、範囲外の電圧VL〜VHで駆動することで、中間電圧VMでの駆動を実現する。

(もっと読む)

電源装置及び電源装置におけるタイミング制御回路

【課題】電源投入時に流れる突入電流を削減すること。

【解決手段】商用電源2から電気機器3に電力を供給する電源装置1において、ON/OFFスイッチ22をONするとタイミング制御回路7で制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を開始し、かつ、ON/OFFスイッチ22をOFFするとタイミング制御回路7Aで制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を終了するようにした。

(もっと読む)

車載情報伝達装置

【課題】インバータの温度を感知する感温ダイオードSDの温度に関する情報をマイコン20に伝達する際に、マイコン20のタイマ機能やA/D変換機能を備えたポートを使用すると、そのリソースが低減すること。

【解決手段】感温ダイオードSDの出力電圧に基づき周波数変調回路34にて周波数変調された信号は、フォトカプラ36に取り込まれる。フォトカプラ36の出力は、マイコン20に取り込まれる。マイコン20においては、フォトカプラ36の出力電圧が閾値電圧以上であるなら論理「H」と認識し、閾値電圧未満であるなら論理「L」と認識する処理を、ハードウェアにて行う。一方、論理「H」である期間や論理「L」である期間に基づく温度情報の復調処理を、ソフトウェア処理とする。

(もっと読む)

電力用素子の故障検出装置

【課題】パワーモジュールに用いられる電力用素子の故障を簡単な構成で検出可能な故障検出装置を提供する。

【解決手段】故障検出装置1Bは、電力用素子としてのIGBTQ1の主電極間の電圧を、ダイオードD7を介して検出する。そして、故障検出装置1Bは、ダイオードD7のアノード電圧が予め定める基準電圧V3より低電圧であるとき、IGBTQ1は短絡故障であると判定する。好ましくは、ダイオードD7のアノード電圧が予め定める基準電圧V4より高電圧であることを併せて判定すれば、フライホイールダイオードD1がオン状態である正常動作の場合を除外できる。

(もっと読む)

ドライバ装置

【課題】トランジスタの異常動作検出と異常信号出力の両機能を備えつつも小型化が図れるドライバ装置を提供する。

【解決手段】外部からの入力信号を受けてトランジスタを駆動制御するドライバ回路と、トランジスタのコレクタに接続されたセンス端子と、センス端子の電位と閾値電圧とを比較するコンパレータと、コンパレータの出力に基づいてセンス端子の電位を保持するラッチ回路と、コンパレータの出力に基づいてタイマー動作を開始するとともに所定時間経過後にセンス端子の電位の保持を解除するためのリセット信号をラッチ回路に出力するタイマー回路とを有し、センス端子の電位に基づいてトランジスタの異常動作を検出するセンス回路と、センス端子に接続され閾値電圧と同じかそれより高い電圧で動作し、異常信号を出力する異常信号出力回路とを備えている。

(もっと読む)

ソリッドステートリレー

【課題】コストの上昇を抑制すると共に、異常動作を防止し、且つスナバ回路の抵抗近傍部品が故障してしまうことを防止することが可能なソリッドステートリレーを提供する。

【解決手段】ソリッドステートリレー20は、スナバ回路Sを構成するコンデンサC0と抵抗R0との接続点dと、トライアックTAのゲート端子Gとを接続する第3接続ライン28cを備えている。さらに、ソリッドステートリレー20は、第3接続ライン28c上に設けられた抵抗R2と、接続点eと接続点bとの間に設けられたコンデンサCとを備えている。

(もっと読む)

周辺光感知回路及びこれを有する平板表示装置

【課題】周囲明るさを正確に感知し、これを利用して周囲の明るさによって自動に画面の明るさを調節することができる周辺光感知回路及びこれを有する平板表示装置を提供することを目的とする。

【解決手段】トランジスタと、トランジスタのしきい値電圧を補償する第1容量性素子と、第1容量性素子に電気的に接続された第2容量性素子と、周辺光が入射されば、第1容量性素子及び第2容量性素子のカップリング電圧を変化させる受光素子と、第1電源の電圧を出力負荷に供給して充電させる第1スイッチと、トランジスタと出力負荷との間に電気的に連結され、第1容量性素子及び第2容量性素子のカップリング電圧に対応してトランジスタを介して出力負荷の電圧が放電されるようにする第2スイッチからなる。

(もっと読む)

半導体リレー

【課題】本発明の課題は、出力段MOSFETのドレイン・ソース間のリーク電流を低減するためベースの不純物濃度を高くしても、ゲート閾値電圧Vtやオン抵抗Ronが増加せず、その結果、スイッチング時間が増加したりオン抵抗が増加したりすることがない半導体リレーを提供することである。

【解決手段】本発明の半導体リレー101は、電気信号を光信号に変換するLED17と、光信号に応じた第一の出力電圧を発生する第1のフォトダイオードアレイ18と、第一の出力電圧がゲート・ソース間に印加されてドレイン・ソース間が導通/非導通状態に切り替えられる出力段MOSFET102,103とを備え、出力段MOSFET102,103のゲート閾値電圧を導通/非導通状態で切替える切替手段104を備えた。

(もっと読む)

半導体装置

【課題】 小さな電流能力しか持たない信号源によるスイッチ制御と保護機能を備えたパワーMOSFETを備えた半導体装置を提供する。

【解決手段】 第1端子にドレインを接続し、第2端子に上記パワーMOSFETのソースを接続し、上記第3端子と上記パワーMOSFETのゲートの間に高抵抗手段を接続する。上記パワーMOSFETに流れる電流を検出する電流検出手段の出力信号を受けて上記パワーMOSFETに流れる電流を制限する電流制限回路を上記パワーMOSFETのゲートと上記第2端子との間に設ける。

(もっと読む)

ゼロクロス検出回路

【課題】

商用電源の交流電圧に対する重畳ノイズ及び波形歪みに対して、ゼロクロスを定周期にかつ安定に検出することができるゼロクロス検出回路を実現する。

【解決手段】

交流電圧がゼロ電位をクロスするタイミングに同期したパルス信号を生成するゼロクロス検出回路において、前記交流電圧の正の半サイクル又は負の半サイクルの少なくともいずれかに同期した矩形波信号を生成する矩形波変換手段と、前記矩形波信号によりトリガされるモノステイブルマルチバイブレータ手段とを備える。

(もっと読む)

インタフェース回路

【課題】光絶縁素子のターンオン時間及びターンオフ時間をともに短縮することで、応答性を向上することができるインタフェース回路を提供することを目的とする。

【解決手段】本発明の入力側サンプリングスイッチは、フォトモスリレーと、トランジスタと、電流制御回路とから構成されている。電流制御回路は並列接続された抵抗及びコンデンサを有している。そして、電流制御回路で、フォトモスリレーをオンさせるときには、オン電流閾値より大きいターンオン電流を、オフさせるときには、ターンオン電流より小さくオン電流閾値より大きいターンオフ電流入力端子に流す。これにより、フォトモスリレーのターンオン及びターンオフ時間を短縮して、入力側サンプリングスイッチの応答性を向上することができる。

(もっと読む)

1 - 20 / 26

[ Back to top ]