Fターム[5J055EX29]の内容

Fターム[5J055EX29]に分類される特許

1 - 17 / 17

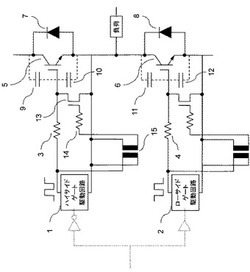

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

半導体集積回路及びそれを備えた駆動装置

【課題】絶縁素子を介した信号伝達に誤動作を生じさせ得る異常を検出して制御対象に停止信号をすることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、外部から供給される送信データVINに応じた送信信号を生成し出力する送信回路Tx1と、受信信号に基づいて送信データVINを再生する受信回路Rx1と、送信回路Tx1と受信回路Rx1とを絶縁するとともに、送信信号を受信信号として伝達する絶縁素子ISO1と、絶縁素子ISO1を介した信号伝達に誤動作を生じさせ得る異常を検出する異常検出部DT1と、異常検出部DT1により異常が検出された場合には、外部から送信回路Tx1に供給される送信データVINに関わらず停止信号を出力する制御部CT1と、を備える。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

ドライバ回路

【課題】回路構成素子数の少ないドライバ回路を提供する。

【解決手段】L1とL2は伝送線路、TRはトランス、TR1とTR2は該トランスの一次側端子、TPは上記トランスの一次側中点タップ、S1とS2は送信回路である。また、Roは伝送線路の終端抵抗である。各々の送信回路は、NPNトランジスタQ1またはQ2、第一の抵抗R1またはR4、第二の抵抗R2またはR5、第三の抵抗R3またはR6からなる。また、T1とT2は、それぞれ、第一と第二の制御入力端子である。さらに、VCCは正電圧源である。そして、上記トランスの一次側中点タップTPは、上記正電源VCCに接続される。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

電源供給装置、情報処理装置

【課題】

サージ電圧を効果的に低減するとともに、簡易な回路構成で消費電力を低減した電源供給装置及び情報処理装置を提供する。

【解決手段】

電源供給装置は、交流電力が入力される入力端子と、前記入力端子に入力される交流電力を整流する整流回路と、前記整流回路で整流された電力を平滑化する平滑用キャパシタと、前記平滑用キャパシタの両端子間に直列に接続される、トランス用一次巻線及びスイッチング素子と、前記トランス用一次巻線に結合されるトランス用二次巻線と、前記トランス用二次巻線に接続される出力端子と、前記スイッチング素子に並列に接続されるスナバ回路であって、第1キャパシタ及び第2キャパシタの並列回路と、前記並列回路に直列に接続される抵抗器とを有するスナバ回路とを含む。

(もっと読む)

ゲート駆動回路

【課題】ゲート駆動信号の伝達遅延時間のばらつきを低減することができるゲート駆動回路を提供する。

【解決手段】ゲート駆動回路1は、トランス2を駆動するトランス駆動回路部3と、トランス2の一次側の駆動タイミングを生成すると共に、入力ゲート駆動信号のON状態時とOFF状態時とでトランス2の一次側駆動電圧変化率を異なるように設定するタイミング生成部4と、トランス2の二次側電圧を微分することで、トランス2の二次側電圧変化率を検出する微分回路部5と、入力ゲート駆動信号のOFF状態時の微分値レベルを検出するレベル検出回路部6と、入力ゲート駆動信号のON状態時の微分値レベルを検出するレベル検出回路部7と、検出レベル検出回路部6,7と接続されたR端子及びS端子を有し、出力ゲート駆動信号を生成・保持するフリップフロップ回路部8とを有している。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

電気回路、充電制御装置、充電システム、および制御方法

【課題】より簡易的な構成で半導体スイッチを駆動する回路を実現する。

【解決手段】充放電切替回路11は、プラス側の電力線に挿入される半導体スイッチ12−1および12−2と、入力側の端子に入力される入力電圧を、所定の出力電圧に変換して出力側の端子から出力する絶縁型DCDCコンバータ23−1および23−2とを備える。そして、絶縁型DCDCコンバータ23−1および23−2の出力側のマイナス端子がプラス側の電力線に接続され、絶縁型DCDCコンバータ23−1および23−2の出力側のプラス端子が半導体スイッチ12−1および12−2の開閉を制御する端子に接続される。本発明は、例えば、高電圧の電源の充放電を制御する回路に適用できる。

(もっと読む)

スイッチ回路および試験装置

【課題】高耐圧のスイッチ回路を提供する。

【解決手段】入力される切替信号に応じて2端子間を電気的に接続するか否かを切り替えるスイッチ回路であって、2端子間を電気的に接続するか否かを切り替える第1切替部と、入力電流に応じて第1切替部を制御する、第1切替部に対して電気的に絶縁された第1制御部と、第1制御部に入力電流を入力するか否かを切り替える第2切替部と、切替信号に応じて第2切替部を制御する、第2切替部に対して電気的に絶縁された第2制御部とを備えるスイッチ回路を提供する。

(もっと読む)

アナログ入力装置

【課題】信号トランスの励磁エネルギーを速やかに消費させ、入力信号のバックスイングおよび各チャンネルの読み込み時間を短縮して、高速化可能なアナログ入力装置を得る。

【解決手段】外部から入力されたアナログ信号を絶縁する信号トランス23と、信号トランス23の1次側に接続され、オンオフ制御されることでアナログ信号をパルス形状に変化させる第1スイッチ素子21と、信号トランス23の1次側に、信号トランス23の巻線端子と並列に接続され、互いに直列に接続された抵抗素子31および第2スイッチ素子32からなるリセット回路22と、第1スイッチ素子21に対して、オンオフ制御のための第1制御パルス信号を出力するとともに、第1制御パルス信号を出力した後に、第2スイッチ素子32に対して、信号トランス23の巻線に励磁されたエネルギーを消費するための第2制御パルス信号を出力する第1、第2シーケンス手段41、42とを備える。

(もっと読む)

容量性信号結合を用いた高電圧駆動回路及び関連する装置及び方法

【課題】ほぼ1つの面内に形成された駆動電極と感知電極とを備えた高電圧駆動回路を提供する。

【解決手段】装置は、駆動回路と感知回路との間の信号の転送を、駆動電極および感知電極を介して容量性手段によって行い、かつIGBTなどの高電圧装置を高電圧トランジスタを使用せずに駆動することが可能にされ、これにより高電圧ゲート駆動回路及びICを製造する場合、SOIなどの高価な製造工程を使用する必要がなくなる。

(もっと読む)

アナログ/ディジタル変換装置

【課題】低オフセットで高価な電圧源を不要にし、低コスト化を可能にした高精度のアナログ/ディジタル変換装置を提供する。

【解決手段】3相交流電圧または交流電流の第1〜第3のアナログ検出値にそれぞれ同一の直流量を加算する手段と、前記直流量加算後の第1〜第3のアナログ検出値を第1〜第3のディジタル検出値に変換する片極性のA/D変換器33と、第1のA/D変換値を(2×第1のディジタル検出値−第2のディジタル検出値−第3のディジタル検出値)/3により演算し、第3のA/D変換値を(2×第3のディジタル検出値−第1のディジタル検出値−第2のディジタル検出値)/3により演算し、第2のA/D変換値を(−第1のアナログ/ディジタル変換値−第3のアナログ/ディジタル変換値)により演算する手段(ソフトウェア)と、を備える。

(もっと読む)

スイッチング電源装置

【課題】簡単な構成で、MOSFETのスイッチングロスをより低減して効率よく、かつ高速でスイッチングすることができるとともに、ハーフブリッジ型のスイッチング回路においてもMOSFETの貫通電流による破損を確実に防止することができるスイッチング電源装置を提供する。

【解決手段】ハーフブリッジ型のスイッチング回路S1、S2において、パルス電圧により駆動するハイサイド側およびローサイド側のMOSFET6、14で直流電源3をスイッチングする際に、一方のMOSFETのOFF遅れによるハイサイド側およびローサイド側の同時ON状態を回避する。

(もっと読む)

ノイズ除去回路、絶縁トランスを用いた信号伝送回路および電力変換装置

【課題】ノイズが連続して到来した場合においても、入力信号に重畳されるノイズの影響を低減しつつ、低圧側と高圧側とを電気的に絶縁しながら信号の授受を行えるようにする。

【解決手段】ノイズ除去回路NU1、ND1は、各ゲートドライブ用PWM信号SU0、SD0のパルス幅が所定値以下の場合、各ノイズ除去回路NU1、ND1は、現在の出力状態をハイレベルまたはロウレベルにそのまま維持し、ゲートドライブ用PWM信号SU0、SD0のパルス幅が所定値を越えると、ゲートドライブ用PWM信号SU0、SD0の立ち上がりおよび立ち下がりに基づいて出力状態をハイレベルとロウレベルとの間で遷移させることで、ゲートドライブ用PWM信号SU0、SD0に重畳されたノイズを除去する。

(もっと読む)

ハイサイド駆動回路

【課題】比較的簡易な構成で、ハイサイドスイッチを高速かつ効率的に駆動するためのハイサイド駆動回路を提供する。

【解決手段】トランジスタQ7,Q8、ダイオードD1,D2、キャパシタC1,C2、変圧器T1によりトリガ信号生成部を構成し、PWM信号をトリガ信号に変換する。ダイオードD3とキャパシタC3によりブートストラップ部を構成し、ハイサイド用電源としてNチャネルトランジスタQ5を高速にオン・オフさせる。抵抗R1,R2、ダイオードD4〜D8、トランジスタQ1,Q2、NチャネルトランジスタQ3,Q4は、ハイサイド用の駆動信号生成部を構成し、トリガ信号V3を、NチャネルトランジスタQ5をドライブするための駆動信号に変換する。

(もっと読む)

ゲート駆動回路への信号伝送方式

【課題】電力変換器の各アーム毎に複数個直列接続される半導体スイッチング素子にオン,オフ信号を供給する場合に、各ゲート駆動回路を互いに縦続接続して伝送により順次供給する構成とすることで、絶縁トランスの容量を小さくし得るようにする。

【解決手段】電力変換器の各アーム毎に、例えばIGBT1〜4を複数個直列接続し、低圧側のゲート駆動回路24から高圧側ゲート駆動回路21まで、絶縁トランス14〜11を介し制御装置10から順々にオン,オフ信号を伝送する構成とすることにより、高圧側の絶縁トランス11の一次巻線と二次巻線間に印加される電圧を従来方式のものよりも低減させ、絶縁トランスの小容量化を図る。

(もっと読む)

1 - 17 / 17

[ Back to top ]