Fターム[5J055FX26]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 時限用コンデンサを有する (279) | 定電流源で充電するもの (5)

Fターム[5J055FX26]に分類される特許

1 - 5 / 5

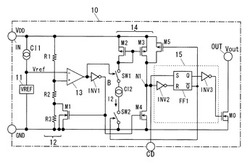

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

タイマー回路

【課題】小さなコンデンサ容量で精度良く長時間設定のできるタイマー回路を実現する。

【解決手段】本発明のタイマー回路は、周期的にオン/オフを繰り返すスイッチ制御信号Voscに基づいて断続的に一定値の電流Iref2を生成し出力する定電流源11と、一端が定電流源11の出力に接続され、他端がVssに接続され、定電流源11からの出力電流Iref2の電荷を蓄積するコンデンサC2と、コンデンサC2の両端の電圧Vc2を入力回路しきい値と比較するインバータINV1を有する。

(もっと読む)

出力回路

【課題】半導体集積回路装置に搭載される出力回路に関し、出力バッファのトランジスタのスレッショルド電圧のばらつきによる外部出力信号のスルーレートのばらつきを抑制できるようにする。

【解決手段】プリバッファ58は、内部出力ノード14とPMOSトランジスタ10のドレインとの間に制御信号電圧変化調整回路59を接続する構成とする。制御信号電圧変化調整回路59は、出力バッファ8のNMOSトランジスタ15のスレッショルド電圧のばらつきによる外部出力信号SC1のスルーレートのばらつきを抑制するように制御信号SB1の電圧変化を調整する。

(もっと読む)

出力回路

【課題】 オンラインダウンロード機能を備える出力部の2つの入力端子の電圧が互いに相関がない電圧で決定されるので、起動時の突入電流が大きい。この突入電流を小さくするために定常状態での出力部の電圧を0Vにしていたが、過渡的にマイナス電位になるために寄生トランジスタをオンしてしまうという課題を解決する。

【解決手段】 ダウンロード切替デジタル信号でスイッチをオン・オフして一端が基準電位に接続された時定数回路内のコンデンサを充放電する時定数回路の出力を出力部の一方の入力端子に入力して、出力部の他方の入力端子に前記基準電位を印加するようにした。出力部の入力誤差が小さくなるので、これによる過大な突入電流が流れることはない。そのため、定常状態における出力部の電圧を自由に選ぶことができるので、寄生トランジスタをオンさせることもなくなる。

(もっと読む)

1 - 5 / 5

[ Back to top ]