Fターム[5J056CC08]の内容

Fターム[5J056CC08]に分類される特許

1 - 11 / 11

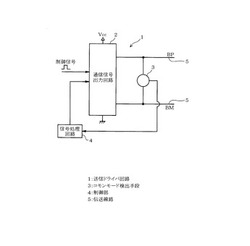

送信ドライバ回路

【課題】信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

出力バッファ回路

【課題】伝送路にノイズが入った場合でも正常に通信ができる通信装置を提供する。

【解決手段】帰還増幅回路(2)と、帰還増幅回路(2)から供給される内部信号に応答して出力ノード(N1)に外部出力信号を供給する出力回路(3)と、帰還増幅回路(2)に対する帰還信号の供給を禁止する帰還遮断回路(4)とを具備する出力バッファ回路(1)を構成する。ここで、帰還増幅回路(2)は、入力端(N2)に入力される送信信号(TXD)と外部出力信号を帰還した帰還信号とに基づいて、内部信号の波形を制御する。そして、帰還遮断回路(4)は、出力ノード(N1)のノイズに基づいて生成される帰還遮断命令に応答して、帰還増幅回路(2)への帰還信号の供給を禁止する。

(もっと読む)

低オフセット入力回路およびそれを含む信号伝送システム

【課題】高速インターフェースに対応可能で、オフセット電圧の低減を実現可能な低オフセット入力回路および信号伝送システムを提供する。

【解決手段】入力回路104および加減算回路ブロック105を含む入力回路ブロック102と、スイッチ108,109、検出回路ブロック106および調整保持回路ブロック107を含むオフセット電圧補償回路ブロック103を設ける。入力回路ブロック102のオフセット電圧を補償する際には、スイッチ108,109をオン動作することで入力回路ブロック102のオフセット電圧を検出回路ブロック106で検出し、この検出したオフセット電圧を調整保持回路ブロック107で保持し、この保持したオフセット電圧を加減算回路ブロック105に負帰還する。これによって、入力回路ブロック102からはオフセット電圧が補償された信号Vop,Vonが出力される。

(もっと読む)

駆動回路

【課題】負荷のリアクタンス成分の変動によって負荷を駆動するための出力の立上り時間が変動した場合であっても負荷の動作が変動するのを抑制する。

【解決手段】負荷Aの容量値が変動した場合、駆動回路1の傾き調整回路6は、電流制御回路50,51のpMOS52及びnMOS53に印加するゲート電圧を調整し、pMOS52及びnMOS53の各ソース−ドレイン間に流れる電流を調整する。つまり、出力ドライバ4のCMOS回路40を構成するpMOS41及びnMOS42のそれぞれのオン時にpMOS41及びnMOS42の各ソース−ドレイン間に流れる電流を調整する。これにより、出力ドライバ4と負荷Aとの間に流れる電流を制御し、負荷Aの容量成分を充放電させる時間を制御するため、負荷Aの駆動電圧の立上り及び立下りの傾きを補正し、上記駆動電圧の立上り時間及び立下り時間を一定時間にする。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

オンダイターミネーションの制御方法及びそれに係る制御回路

【課題】オンダイターミネーションが動作する周波数に関係なく、遅延固定ループクロックと内部クロックとの間のクロックドメインエラーを解決し、所望のタイミングにオンダイターミネーション動作を行うことができるオンダイターミネーション制御方法及びそれに係る制御回路を提供する。

【解決手段】外部クロック及び遅延固定ループクロックを受信して、それぞれのクロックがトグルされる数を設定された値からカウントするカウンタ部と、オンダイターミネーション命令信号に応答し、前記外部クロックカウント値と前記遅延固定ループカウント値とを比較し、その値に応じてオンダイターミネーションの動作を制御する比較制御部とを備える。

(もっと読む)

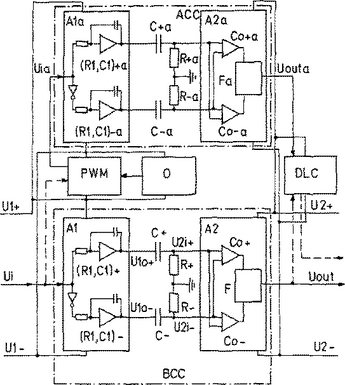

容量性障壁を備えた分離インターフェース及び該分離インターフェースによる信号の伝送方法

容量性障壁を備えた分離インターフェースを通しての信号の伝送が行われると、インターフェースの入力回路において、適切な時定数の積分による容量性障壁を備えた基本分離インターフェースの入力回路によって、伝送された入力信号UiのレプリカであるU1o+とU1o-の端の傾斜変化率または、上昇と減少時間が調整され、そして上記の信号レプリカは適切な微分ユニットで微分されて、これらの微分ユニットの時定数は信号レプリカの上昇と減少時間、よりも短かく、有利には約1ナノセカンドか、またはそれ以下である。したがって、パルス幅を非常に正確に維持できるので、容量性障壁の出力側面の上の回路では、電圧比較器のアンプは全く必要ではない。入力と出力回路に関する電圧供給ソースの間の電位差の約10kV/μsの速い変化から、データ伝送が守られる。本発明によって、100MHzの周波数までのデジタルデータ伝送が可能になる。  (もっと読む)

(もっと読む)

同時双方向回路

【課題】

一の伝送路を介して信号の送受信を行う同時双方向回路において、その同時双方向回路に備えられた送信回路の動作に応答して、受信回路が誤動作してしまうことを防止する技術を提供する。

【解決手段】

同時双方向回路の構成を、送信信号を生成して前記送信信号を入出力端を介して伝送路に出力する送信回路と、前記入出力端に接続され、前記入出力端を介して受信信号を受信する受信回路だけで構成するのではなく、前記送信回路の出力端と前記受信回路の入力端との間に介接され、前記送信回路の出力に応答して、前記受信回路の動作に影響を及ぼす電圧変化に対応する特定信号電圧を生成する特定信号電圧生成回路と、前記送信回路の入力端に接続され、前記特定信号電圧生成回路に基準電圧信号を供給する基準電圧生成回路とを備える構成にする。そして、前記特定信号電圧生成回路は、前記基準電圧信号と前記電圧変化との比較に基づいて特定信号電圧を生成し、前記特定信号電圧を前記受信回路の入力に供給するような同時双方向回路により通信を行うようにする。

(もっと読む)

1 - 11 / 11

[ Back to top ]