Fターム[5J056DD46]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | エンハンスメントとディプレッションの組合せ (5)

Fターム[5J056DD46]に分類される特許

1 - 5 / 5

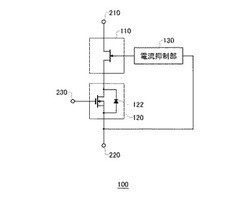

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

低電流の論理およびドライバ回路

低電流回路は、論理ステージ(E3,E4,E5)と、インバータステージ(E8)と、ドライバステージ(E9,E10)とを備える。論理ステージおよびインバータステージには電流リミッタが設けられ、電流リミッタは、Dモードフィードバックトランジスタ(D1;D2)および電圧降下を生成する要素(E1,E2;E6,E7)を備える。フィードバックループ(FL)は、Dモードフィードバックトランジスタのソースおよびゲートを、この要素を介して接続する。ドライバステージは、トーテムポール状に接続されたEモードトランジスタ(E9,E10)を備え、それは、負荷回路を接続および非接続とするように、DモードトランジスタおよびEモードトランジスタを駆動する。この回路は、オン状態において大電流能力を提供するとともに、オフ状態において無視できるほどの電流を有する。  (もっと読む)

(もっと読む)

低電流インバータ回路

本回路は、ゲート・ソース接合を有するEモードトランジスタ(E3)と、ゲート・ソース接合を有するDモードトランジスタ(D)と、Dモードトランジスタのソース(4)とEモードトランジスタのドレイン(2)との間に電圧降下を生じさせる構成要素(E1、E2)と、Eモードトランジスタのドレイン(2)とDモードトランジスタのゲート(6)との間の接続ラインとを備える。Eモードトランジスタのゲート(3)は入力信号(IN)用に設けられ、Eモードトランジスタのドレイン(2)は出力信号(OUT)用に設けられる。本回路は、低電流を流すのみでGaAsテクノロジーにおける論理回路を動作させることができる。  (もっと読む)

(もっと読む)

ED型インバータ回路および集積回路素子

【課題】特性の制御性および高温下での信頼性が高いED型インバータ回路および集積回路素子を提供すること。

【解決手段】基板上に形成された窒化物系化合物半導体からなる第1半導体層と、第1半導体層上に形成されるとともに、所定の位置に開口部を有し、第1半導体層よりもバンドギャップが大きい窒化物系化合物半導体からなる第2半導体層と、第2半導体層の開口部内に露出した第1半導体層の表面に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極と、第2半導体層上の第1ゲート電極を挟む位置に形成され、第2半導体層とオーミック接触する第1ソース電極および第1ドレイン電極と、第2半導体層上に形成され、第2半導体層とショットキー接触する第2ゲート電極と、第2半導体層上の第2ゲート電極を挟む位置に形成され、第2半導体層とオーミック接触する第2ソース電極および第2ドレイン電極と、を備える。

(もっと読む)

電圧レベルシフト回路、および半導体集積回路

【課題】 差動増幅回路の入力に接続され、信号の入力電圧範囲を広げる電圧レベルシフト回路において、電圧レベルシフト回路の出力信号が電源電圧の変動の影響を受けないようにする。

【解決手段】 Pチャネルエンハンスメント型トランジスタM1とNチャネルデプレッション型MOSトランジスタM3で構成される第1の電圧レベルシフト回路と、Pチャネルエンハンスメント型トランジスタM2とNチャネルデプレッション型MOSトランジスタM4で構成される第2の電圧レベルシフト回路を設け、第1の電圧レベルシフト回路に対して直列にNチャネルデプレッション型トランジスタM5を用いたカスコード回路を接続し、第2の電圧レベルシフト回路に対して直列にNチャネルデプレッショント型ランジスタ6を用いたカスコード回路を接続し、各カスコード回路のバイアス電圧を相補に制御する手段を設ける。

(もっと読む)

1 - 5 / 5

[ Back to top ]