Fターム[5J056DD54]の内容

Fターム[5J056DD54]に分類される特許

1 - 12 / 12

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積とコストの増加や、電気的特性の問題を招くことなく、出力バッファ回路の出力電圧のリンギングを抑制する。

【解決手段】半導体集積回路200は、電源線10、電源抵抗11、接地線12、接地抵抗13、出力バッファ回路14,15,16、電源端子PVdd、接地端子PVss、出力端子PO1,PO2,PO3、及びリード端子17,18を含んで構成される。電源抵抗11は、電源線10と出力バッファ回路14の電源電位入力端との接続点N1と電源端子PVddとの間に接続されている。接地抵抗13は、接地線12と出力バッファ回路14の接地電位入力端との接続点N4と接地端子PVssとの間に接続されている。

(もっと読む)

半導体装置

【課題】従来技術において、制御回路に発生する電源ノイズを出力バッファに影響させないようにするには、出力バッファと制御回路の電源ラインを別々に設ける方法があった。しかし、この方法には、電源・グランドピン数の増加、給電ラインインダクタンスの増加といった問題があった。

【解決手段】本発明では、上記課題である(1)電源・グランドピン数増加と(2)給電ラインインダクタンスの増加を生じることなく、制御回路で問題となるノイズが出力バッファに回り込まないような技術を提供する。具体的な手法は、(A)制御回路用のオンチップバイパスキャパシタンスを設け、AC的に制御回路と出力バッファの給電経路を切り分ける方法、と(B)給電経路の電気パラメータノイズの振動モードが過減衰になるような設計(抵抗の挿入)をする方法がある。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

半導体集積回路

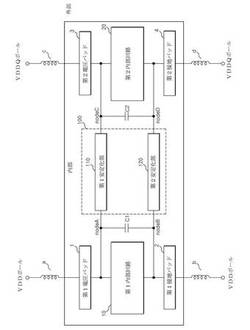

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電圧パッド1、第2電圧パッド3、及び前記第1電圧パッド1と前記第2電圧パッド3との間に接続された電圧安定化部100を含み、前記第1電圧パッド1は、第1内部回路10に接続され、前記第2電圧パッド3は、第2内部回路20に接続されることを特徴とする。

(もっと読む)

半導体装置および電源補償方法

【課題】ロジック回路の高速動作に伴う電源変動を抑制する。

【解決手段】第一配線と第二配線との間に第一線間電圧が与えられ、該第一配線と第三配線との間に該第一線間電圧以上の第二線間電圧が与えられ、該第三配線と該第一配線との間に設けられた第一容量値を有する容量素子と、該容量素子と該第三配線との間に設けられ該第三配線から該容量素子へ流れる電流を制限する電流制限部と、該第二配線と該容量素子との間に接続した第一スイッチ素子と、該第一線間電圧に応じて該第一スイッチ素子を制御する電圧検出部とを有することを特徴とする。

(もっと読む)

並列接続トランジスタ

【課題】配線のための面積増加なしに各トランジスタの入力信号の強度及び位相を均一にできる並列接続トランジスタを提供する。

【解決手段】並列接続トランジスタ50は、信号入力端子60に接続される伝送線路70、72と、伝送線路70及び72に沿って一列に配列されたトランジスタ84−1〜84−8及び88−1〜88−8と、伝送線路70、72に沿って一列に配列され、伝送線路70、72に一端が接続され、トランジスタ84−1〜84−8及び88−1〜88−8の対応する1つのベース端子に他端が接続された複数の容量素子82−1〜82−8及び86−1〜86−8とを含み、容量素子82−1〜82−8及び86−1〜86−8の容量値は、信号入力端子60からの伝送線路の線路長が大きいほど、小さくなっている。

(もっと読む)

基準信号供給装置

【課題】パッケージ内部のクロストークによる基準信号への影響を無くすようにした基準信号供給装置を提供する。

【解決手段】ICパッケージ1と基準信号発生部3との間を、ICパッケージ1の特性インピーダンスに比して低い特性インピーダンスの伝送線路2により接続してICパッケージ1から基準信号発生部3側を見た場合に、見かけ上の電気長が無限大になるようにし、かつICパッケージ1で発生したクロストークによる信号をICパッケージ1内に送り返すようにして、ICパッケージ1内でクロストークによる信号の相殺ループを形成するようにし、また伝送線路2を通過した高周波成分つまり交流成分の信号を伝送線路2と直列に接続した抵抗Rにて吸収するようにしている。

(もっと読む)

リンギング低減回路および該リンギング低減回路を備えた半導体集積回路

【課題】 動作速度を犠牲にせず、半導体集積回路の出力信号のリンギングを低減する。

【解決手段】 リンギング低減回路40NAは、出力信号線120および低電位電源線112間のNチャネルトランジスタ401と、コンパレータ410とを有する。コンパレータ410は、出力信号OUTを高電位電源線111のレベルPVDDIと比較し、出力信号OUTがレベルPVDDIを越えるオーバシュートが発生しているとき、Nチャネルトランジスタ401をON状態とし、オーバシュートを低減する。リンギング低減回路40PAは、同様の原理により、出力信号OUTのアンダシュートを低減する。

(もっと読む)

バス回路及び半導体回路

【課題】波形品質の劣化、電源バウンス、及び電磁波放射を抑制して、高速動作を実現すると共に、使用ピンの数の増大及び回路規模の拡大を抑制することができるようにする。

【解決手段】バス回路10は、伝送線路12と、伝送線路12の送信端に接続されたオープンドレインのPMOS素子からなる駆動スイッチング回路14と、一端が伝送線路12の受信端に接続された終端抵抗16と、インダクタンス成分を有する接続回路20を介して、終端抵抗16の他端に接続され、終端電位となっている電源22と、終端抵抗16の一端に接続され、かつ、信号を受信するためのレシーバ素子18とを備える。バス回路10は、ドレインが、終端抵抗16を迂回するように接続回路20を介して電源22に接続され、ソースが接地されているNMOS素子からなる迂回スイッチング回路24を備え、迂回スイッチング回路24のゲートは伝送線路12の受信端に接続されている。

(もっと読む)

高い電圧供給レベルを用いた低電圧論理回路オペレーション

【課題】各モジュール間の電流消費の基を減少させ、損失の低減を図る。

【解決手段】回路であって、第1及び第2基準電位の間に直列に接続された2n個のモジュール30,34を備え、2n−1個のノード52は2n個のモジュール30,34の隣接する複数のモジュールの間に配置され、それぞれの2n−1個の2:1DC/DCコンバータ100は、2n−1個のノードのうちのそれぞれ1つと連通し、モジュール間の電流の不一致を制御する。

(もっと読む)

1 - 12 / 12

[ Back to top ]