Fターム[5J104JA09]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 暗号方式(一方向性関数も含む) (6,548) | 対称暗号系(共通鍵暗号系) (4,021) | 換字と転置を交互に繰り返すもの (212) | Feistel型暗号 (147)

Fターム[5J104JA09]の下位に属するFターム

L−type

R−type

B−type (73)

非線形関数に表引きを使用するもの (5)

非線形関数に表引を使用しないもの

Feistel暗号の合成演算 (9)

Fターム[5J104JA09]に分類される特許

41 - 60 / 60

共用のハードウェアを利用して暗号文及びメッセージ認証コードを生成するための方法及びシステム

【課題】

共用のハードウェアを利用して暗号文およびメッセージ認証コードを生成するための方法およびシステムを提供する。

【解決手段】

第1および第2認証済み暗号化ハードウェア・モジュールを含む認証済みの暗号化ユニットにおいて、平文のメッセージ・データが受け取られる。しかる後、第1認証済み暗号化モードと関連した第1メッセージ認証コード(MAC)および第2認証済み暗号化モードと関連した第2MACが生成される。平文のメッセージ・データおよび第1認証済み暗号化ハードウェア・モジュールを利用して第1MACが生成され、平文のメッセージ・データおよび第2認証済み暗号化ハードウェア・モジュールを利用して暗号文のメッセージ・データおよび第2MACが生成される。

(もっと読む)

データ処理装置、およびデータ処理方法

【課題】小さな回路規模で、複数チャネルのリアルタイムデータの暗号化処理(または復号化処理)が可能なデータ処理装置を提供する

【解決手段】各入力チャネルごとに設けられた入力バッファ121〜123に、入力されたデータをそれぞれ格納する。演算チャネル制御部130は、入力データセレクタ140を制御して、入力バッファ121〜123に格納されているデータを、時分割して演算回路110に対してブロック単位で入力する。演算回路110は、暗号鍵セレクタ150から与えられた暗号鍵で入力されたデータを暗号化(または復号化)して出力する。

(もっと読む)

暗号化/復号化装置、電子機器及び暗号化/復号化方法

【課題】 製造メーカ側に対し機密情報を秘匿でき、且つ低コストでコンテンツデータを保護できる暗号化/復号化装置、電子機器及び暗号化/復号化方法を提供する。

【解決手段】 暗号化/復号化装置10は、第1のアルゴリズムに従ってコンテンツデータの暗号化/復号化処理を行う暗号化/復号化回路16と、第2のアルゴリズムに従って暗号化された状態で外部メモリ20に記憶されている暗号化/復号化処理用の暗号化/復号化情報が該外部メモリから読み出された場合に、該暗号化/復号化情報に対し前記第2のアルゴリズムに従って復号化処理を行う復号化回路12と、復号化回路12によって復号化された暗号化/復号化情報を記憶するメモリ14とを含む。暗号化/復号化回路16は、コンテンツデータに対し、メモリ14に記憶された暗号化/復号化情報に基づいて暗号化/復号化処理を行う。

(もっと読む)

送受信システムおよび方法、送信装置および方法、受信装置および方法、並びにプログラム

【課題】鍵が所定の更新周期で更新されながらストリームデータが暗号化される場合、その更新周期を可能な限り短縮させることができるようにする。

【解決手段】 例えば、ストリームデータの暗号化に利用された1つの鍵を含む38バイトのデータをLEKPと称し、このLEKPが、2048ビット(=256バイト)のデータを利用するRSA暗号に従った暗号化処理が施された上で、復号側に伝送されるとする。この場合、1つのLEKP(1)だけではなく、さらに、その他のLEKP(2)乃至LEKP(6)を代入した上で、即ち、LEKP(1)乃至LEKP(6)が連続して配置されたデータを生成した上で、RSA暗号に従った暗号化処理を施す。本発明は、AVデータを暗号化する暗号化装置と、それに対応する復号装置とからなるシステムに適用可能である。

(もっと読む)

データ変換装置及びデータ変換方法及びデータ変換方法をコンピュータに実行させるプログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】Sボックス第1変換部13とSボックス第2変換部14の構成を、安全性を保持しつつ簡単な構成とする。

【解決手段】データを非線形変換する非線形データ変換部280は、変換するデータの一部分のデータを第1部分データとして入力して、入力したデータの値を他の値に変換して出力する変換テーブルTを用いて第1部分データを変換し、変換したデータを出力するSボックス第1変換部13(s1)と、変換するデータの少なくとも他の一部分のデータを第2部分データとして入力して上記変換テーブルTを用いた変換と第2部分用演算とを用いて第2部分データを変換し、変換したデータを出力するSボックス第2変換部14(s2)とを備えた。

(もっと読む)

データ変換装置、プログラム、記憶媒体

【課題】 AESのような、ガロア体(有限体)上の演算処理を有するブロック暗号において、処理速度が高速であり、かつ従来方式よりも少ない記憶容量で処理可能な方式を提案する。

【解決手段】 換字テーブルと排他的論理和の組み合わせにより、換字テーブル用記憶容量を減少させる。

即ち、Nバイト(ビット)*1個の基礎となる事前計算データと、1バイト(ビット)*A個(Aの個数は利用する暗号の処理体系に依存)の事前計算データ及びexclusive orのような論理演算を用いる。

(もっと読む)

ストリーム暗号化装置、ストリーム暗号化方法、ストリーム復号化装置、ストリーム復号化方法

【課題】コンテンツとしてのストリームを高速に暗号化・復号化する。

【解決手段】コンテンツ送信装置の暗号器は、ストリーム(コンテンツ)を所定のパケット単位で並列的に暗号化する。ここで、暗号器は、入力データ蓄積部(FIFO)と出力データ蓄積部(FIFO)と、これらの間に、複数の暗号化部と、複数の暗号化部に対応してそれぞれの入力側のデータ蓄積部(FIFO)群および出力側のデータ蓄積部(FIFO)群とを備え、基準ブロック単位のデータを順次処理することで高速に暗号処理する。同様にして、コンテンツ受信装置の復号器は、受信したパケット単位の暗号化データを並列的に復号化する。

(もっと読む)

ラインドールブロック暗号化装置、及びその暗号化並びに復号化方法

本発明は、ラインドールブロック暗号を暗号化及び復号化するためのラウンド演算を效率よく行う演算装置を含んだラインドールブロック暗号化装置とその暗号化及び復号化方法に関する。本発明に係るラインドールブロック暗号化装置は、高速、小面積の暗号プロセッサーを要求する携帯電話やPDAのような携帯電話端末またはスマートカードに搭載することにより、保安を要する重要なデータを高速で暗号化及び復号化でき、特に、128ビット入力データを上位64ビットと下位64ビットに分けて、ラウンド演算を行うようになっている。したがって、本発明は、ラインドールブロック暗号を暗号化及び復号化するのに必要な時間を減らしながら、装置の面積を減少させることができる。  (もっと読む)

(もっと読む)

暗号/復号装置及び方法

秘守性に優れ、エラーから完全に復帰できる暗号化を行う。入力映像データがEXOR100で疑似乱数列と演算されて得られた暗号化データがFF101にホールドされ、ライン毎にリセットされる。カウンタ102及び103は、夫々ライン毎及びフレーム毎に計数され、フレーム毎及びプログラムの先頭でリセットされる。暗号器105は、固定値をホールドするFF104、カウンタ103、102及びFF101の出力を鍵(K)を用いて暗号化して疑似乱数列を発生させ、シフトレジスタ106でビット列を分割する。シフトレジスタ106の出力と入力映像データとがEXOR100で演算され、暗号化データが得られる。暗号出力をフィードバックするので同一データの連続入力を利用したデータ窃取が行えないと共に、フィードバックする暗号出力がライン毎にリセットされるので、エラーから完全に復帰できる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】AES方式の暗号化及び復号化における処理を、論理回路を中心とするハードウェアと、ソフトウェアに基づいて動作するマイクロプロセッサとに分担させることによって、所望の処理スループットを実現しつつ回路規模又は消費電力を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路で、暗号処理において用いられる少なくとも1つの鍵及び複数の制御信号を生成するマイクロプロセッサと、複数の入力データ群と複数の帰還データ群との内の一方を選択する選択回路と、選択回路から出力される複数のデータ群を格納する格納回路と、前処理として複数の帰還データ群を生成して帰還ループに供給すると共に、その後、複数の帰還データ群を順次用いて行った演算結果を変換テーブルを参照して変換することにより複数の入力データ群に対して暗号化又は復号化処理を施す論理回路とを具備する。

(もっと読む)

暗号化/復号化装置、通信コントローラ及び電子機器

【課題】 暗号化及び復号化処理の負荷を分担することでスループットを向上させる暗号化/復号化装置、通信コントローラ及び電子機器を提供する。

【解決手段】 暗号化/復号化装置100は、入力データ及び出力データが格納される記憶部110、第1の暗号化及び復号化処理を行う第1の暗号化/復号化処理部120、第2の暗号化及び復号化処理を行う第2の暗号化/復号化処理部130を含む。入力データに対し第1及び第2の暗号化/復号化処理部120、130の一方が行った第1又は第2の復号化処理後の復号化データを記憶部110に格納する。復号化データに対し第1及び第2の暗号化/復号化処理部120、130の他方が行った第1又は第2の暗号化処理後のデータを出力データとして記憶部110に格納する。記憶部110の復号化データの記憶領域が、暗号化/復号化装置100の外部からアクセス不可となるように構成される。

(もっと読む)

ドキュメント処理装置とその装置にデータ暗号化サービスを追加する方法およびプログラム

【課題】ドキュメント保護が強化されたドキュメント処理装置とこの装置にデータ暗号化サービスを追加する方法およびプログラムを提供する。

【解決手段】ドキュメント処理装置は2つの択一的暗号化メカニズムを含む暗号化イネーブルソフトウェアを受け取り、暗号化するドキュメントファイルのユーザによる選択を待って、利用可能な暗号化メカニズムの一つを使用してそのファイルの暗号化を行う。ドキュメントファイルの暗号化は、例えば、トリプルDESによって行う。

(もっと読む)

暗号化関数を難読化するための方法及びシステム

システム300において、サーバ310は、難読化形式により暗号化関数Fを実行装置に提供する。関数Fは、アーベル群演算子

【数221】

を用いて複数のマッピングテーブルTi(0≦i≦n;n≧1)の出力を構成する。プロセッサ312は、

【数222】

となるようにテーブルOとCを選択し、テーブル

【数223】

を生成する。ただし、0≦i≦nに対して、各テーブルT’iは各自の対応するテーブルT,jを表し、少なくとも1つのテーブル

【数224】

がTo1とOのアーベル合成により形成され、少なくとも1つのテーブル

【数225】

がCを含むアーベル合成により形成される。手段314は、テーブルT’iを実行装置に提供するのに利用される。実行装置320は、テーブルを受け付ける手段324と、テーブルT’iのアーベル合成により暗号化関数Fに機能的に等価な関数F’を形成するプロセッサ322とを有する。

(もっと読む)

(もっと読む)

sボックス

多入力多出力のsボックスであって、a個の隣接番号の入力ビット(101,102,103,104,105)I1、I2乃至Iaを受信し、ここでaは少なくとも4であり、b個の連続番号の出力ビット(131,132,133,134,135)O1、O2乃至Obを出力する。このsボックスは、c個の一次sボックス(121,122,13)sb1、sb2乃至sbcを含む。各一次sボックス(121,122,123)は多入力単一出力のブール関数f1、f2乃至fcを具え、これらが多入力と単一出力の関係を規定する。各一次sボックス(121,122,123)はそれぞれ入力ビットs1、s2乃至scのセットを受信し、これらのセットがそれぞれ前記sボックスへのa個の入力ビット(101,102,103,104,105)から選択され、それぞれsl1、sl2乃至slcビットを含む。前記sl1、sl2乃至slcの数は3乃至(a−1)の範囲内にあり、前記sl1、sl2乃至slcの数の合計がaより大きい。前記sボックスのb個の出力ビット(131,132,133,134,135)が、前記c個のブール関数の出力を含む。 (もっと読む)

暗号回路および集積回路

【課題】ノイズ発生器等の差分電力解析に対抗する手段は暗号回路の外部に実装されるため、暗号回路単体に対する差分電力解析への対抗する手段がない。また、暗号アルゴリズムに抜本的な差分電力解析対策を施す場合、必要なハードウェアコストが大きくなる。

【解決手段】秘密鍵に対して部分鍵演算を16回繰り返し実行して部分鍵K1〜K16を生成し、部分鍵K1〜K16および平分2Bを入力してラウンド演算を16回繰り返すことにより、平分2Bを暗号化する。この場合、いずれかD回のラウンド演算によって得られた信号と部分鍵を入力してダミー演算をD回実行する。

(もっと読む)

暗号化装置、暗号化方法及び復号化装置、復号化方法

【課題】 処理速度を維持しながら回路をより小型化できる暗号化装置を提供する。

【解決手段】 各々が演算の段階ごとに設けられたπ1回路101〜π4回路104、π1回路101〜π4回路104の各々に対応して設けられ、演算の結果を保持するレジスタ105a〜105dで演算ユニット106aを構成する。演算ユニット106aにおいて、π1回路101は、2つの入力データを使って演算し、データを生成する。レジスタ105aは、生成されたデータを保持する。π2回路102は、レジスタ105aによって保持されているデータとπ1回路101に入力されたデータの一つとを使ってデータを生成し、このデータをレジスタ105bが保持する。π3回路103は、レジスタ105bによって保持されているデータとπ2回路102に入力されたデータの一つとを使ってデータを生成し、このデータをレジスタ105cが保持する。

(もっと読む)

暗号処理装置および暗号処理方法

【課題】中断/再開機能を効率的に行うことが可能な暗号処理装置および暗号処理方法を提供する。

【解決手段】DMAC14がデータ格納メモリ12から処理すべき転送データを指示する情報となるDMAディスクリプタに、DESやAESといった共通鍵暗号の暗号アルゴリズムを指示するフィールドと、ECBモードやCBCモードやCounter Modeといった暗号処理モードを指示するフィールドとを有するディスクリプタフォーマットになっている。また、DMAC14がデータ格納メモリ12から処理すべき転送データを指示する情報となるDMAディスクリプタに、MD5やSHA−1といったハッシュアルゴリズムを指定するフィールドと、ハッシュ処理の中断の指示するフィールドと、ハッシュ処理の再開を指示するフィールドとを有するディスクリプタフォーマットになっている。

(もっと読む)

暗号化回路装置及び方法

暗号化アプリケーション用の列変換をXOR演算を用いて実行する。本発明の一実施例では、入力列のバイトをAESアルゴリズム用に変換する(110,120,130)。出力列の変換されたバイトは、入力列の各バイトからの少なくとも1ビットを論理的に組み合わせる(XOR演算する)ことにより生成する(120)。変換されたバイトはAESアルゴリズムのためのMixColumn変換を満すため、MixColumn変換に使用される論理的組み合わせ及び乗算の代わりに上述の論理的組み合わせを使用することができる。このアプローチによれば、MixColumn変換に指定されている有限フィールド乗算を回避し、等価な変換を単一タイプの論理組合せのみを用いて実行することができる。  (もっと読む)

(もっと読む)

各暗号化ラウンドのコア暗号化関数を隠蔽するために置換を用いたブロック暗号化システム

システム(600)において、サーバ(610)は、ディジタル信号処理関数fを不明瞭化された形態で実行装置(620)に供給する。関数fは、信号処理関数fi(1≦i≦N)の関数縦続を式(I)に含める。前記サーバは、2N個の反転可能な置換piのセット(1≦i≦2N)を選択し、N個の関数giのセットを算出し(giは1≦i≦Nについて式(II)に関数的に同等である)、N−1個の関数hiのセットを算出する(hiは2≦i≦Nについて式(III)に関数的に同等である)ためのプロセッサ(612)を含む。前記サーバは、式(IV)を含む実行装置関数縦続を実行装置に備えるための手段(614)を含み、ここでy1、・・・、yNは式(V)に対する関数パラメータであり、前記サーバは更に、関数g1、・・・、gNを前記実行装置に供給するための手段(616)を有する。前記実行装置は、関数g1、・・・、gNを取得する手段(626)と、前記実行装置関数縦続をロードし該ロードされた実行装置関数縦続を関数g1、・・・、gNに適用する(例えばEDi(g1,・・・,gN))ためのプロセッサ(622)とを含む。  (もっと読む)

(もっと読む)

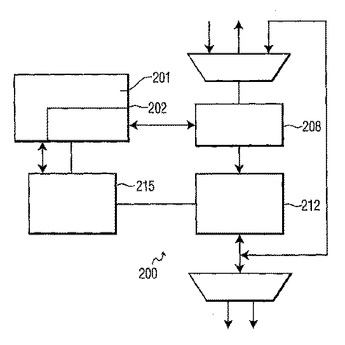

鍵拡大機能の低メモリハードウェア実施のための方法および装置

AES等のアルゴリズムにおける鍵拡大機能中に必要とされるメモリ空間を減らすための装置、方法、コンピュータプログラム。所定数のバイト単位を暗号文/平文に暗号化/復号化するためのブロックラウンドユニット(212)。鍵拡大モジュール(215)は、拡大鍵値を得るために通常(暗号化)機能および逆(復号化)機能の両方に関して鍵拡大を実行する。拡大鍵値の格納のために必要とされるメモリ(202)内のメモリ空間の数は、拡大鍵値の数の半分よりも多くなく、一般に、14個の鍵においては、鍵値およびメモリ空間の数が等しい場合に対してアクセス時間を増大させることなく、7個のメモリ空間を必要とする。鍵拡大はラウンド鍵処理と同期して行なわれ、それにより、各鍵拡大毎に、ラウンド鍵が対応する鍵拡大機能と並行して処理される。  (もっと読む)

(もっと読む)

41 - 60 / 60

[ Back to top ]