Fターム[5J106BB06]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 電動機器 (6)

Fターム[5J106BB06]に分類される特許

1 - 6 / 6

モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

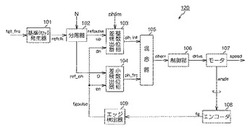

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

(もっと読む)

アクチュエータの駆動装置ならびにそれを用いる平行移動機構、干渉計および分光器

【課題】被駆動部材となる可動部とそれを駆動する駆動部とを備えて成るアクチュエータをPLL回路で駆動し、機械共振駆動を行わせる駆動装置において、短時間でかつ確実な位相引き込み動作を可能にし、さらに回路規模の増大やコストアップを抑える。

【解決手段】PLL回路のループフィルタ部14aを、位相比較器13の位相比較信号Vpdを平滑化してVCO11へ制御電圧Vcとして与えるLPFとしての機能を実現する積分回路21に、基準電圧源22とリセット手段としての短絡スイッチ23とを設ける。したがって、前記制御電圧Vcは、積分動作に伴い、基準電圧Vrefから共振周波数の目標電圧付近に滑らかに移行するので、オーバーシュートやリンギングの発生がなく、短時間でかつ確実な位相引き込み動作(位相ロックイン)を行うことができる。また、PLLループの外部に、制御信号を掃引するための特別な構成を設ける必要もない。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御に対して、多重PLL回路を適用可能な回路構成を得る。

【解決手段】発振信号を出力する発振器12及び該発振信号と入力信号との位相差に対応する信号を出力する第1位相比較回路14を有する第1PLL11と、入力に応じて回転制御され且つ回転子の回転位置を信号出力するモータ部22及び該モータ部22からの出力信号と入力信号との位相差に対応する信号を出力する第2位相比較回路24を有する第2PLL21と、上記第1PLL11及び第2PLL21が上記入力信号の入力側に対して互いに並列に接続されるように、互いの位相比較回路14,24の出力同士を加算する加算器26と、を備える。上記第1PLL11の発振器12の入力側及び上記第2PLL21のモータ部22の入力側には、それぞれ、ループフィルタ15,25を設ける。

(もっと読む)

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

クロック発生回路

【課題】同期回路を含む電子機器の電池電圧が低下してきた場合に、その電子機器の動作維持に対応できる上に、その構成が簡易であるクロック発生回路の提供。

【解決手段】カウンタ回路14は、基準クロック発生回路11からの基準クロックSCLKの1周期内において、リングオシレータ13からのパルスRCLKをカウントする。ここで、このパルスRCLKの周波数は、電源3の電圧値を反映させたものとなり、そのカウント値もそれを反映させたものとなる。分周制御回路15は、カウンタ回路14のカウント値に従って、クロック分周回路12の分周比を設定する。クロック分周回路12は、その設定された分周比に応じて、基準クロック発生回路11からの基準クロックSCLKを分周させて、その周波数を低下させる。

(もっと読む)

1 - 6 / 6

[ Back to top ]