Fターム[5J106GG12]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 合成・分配回路 (11)

Fターム[5J106GG12]に分類される特許

1 - 11 / 11

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

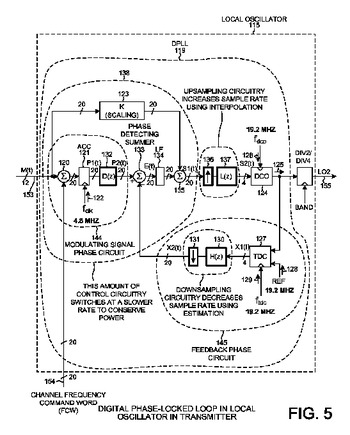

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

可変分周器および検波器

【課題】可変分周器の出力信号のデューティー比を任意の比率に設定する。

【解決手段】入力クロックを予め設定された分周比で分周した分周クロックを出力する可変分周器であって、入力クロックを分周した内部クロックを出力する分周部と、内部クロックを2分周して分周クロックとして出力する固定分周器と、分周クロックの論理値に応じて第1分周比および第2分周比のいずれかを選択し、分周部が入力クロックを分周する分周比として設定する選択部とを備える可変分周器を提供する。

(もっと読む)

位相ロックループ内でのキャパシタンス乗算のための方法および装置

2つのチャージポンプを用いるキャパシタンス乗算のための方法および装置である。第1のチャージポンプ(206)は、RCネットワークの抵抗器(310)によってまず伝えられ、次いで、RCネットワークのキャパシタによって伝えられる前に3つの電流路に分離される電流信号(I216)を供給する。第1の電流路は、ノード(320)からRCネットワークのキャパシタ(306)に電流を供給する。第2の電流路は、キャパシタ(306)が伝える電流を、第1の電流乗算係数で乗算する。第3の電流路は、第1の電流乗算係数に対して逆の大きさの符号を有する小数値を有する第2の電流乗算係数で第1のチャージポンプ(206)からの電流を乗算する第2のチャージポンプ(208)に電流を供給する。第2および第3の電流路の組合せにより、キャパシタ(306)のキャパシタンスの大きさは効果的に乗算される。  (もっと読む)

(もっと読む)

PLL過渡応答制御システム及び通信システム

【課題】外部制御信号によってPLL回路の周波数を変更したときの過渡応答時間の短縮が可能なPLL過渡応答制御システムを提供する。

【解決手段】2系統のPLL回路を備え、一方のPLL回路には制御電圧が高くなるほど発振周波数が高くなる電圧制御発振器VCO1が使用され、かつ、他方のPLL回路には制御電圧が高くなるほど発振周波数が低くなる電圧制御発振器VCO2が使用され、一方の電圧制御発振器VCO1への帰還電圧が他方の電圧制御発振器VCO2への帰還電圧に加えられ、2つの電圧制御発振器VCO1,VCO2の出力信号がミキサー13で合成されることにより、2つのPLL回路の過渡応答が相殺されてミキサー13の出力信号の過渡応答が速くなる。

(もっと読む)

デジタルシステム

【課題】PLL回路が発生するクロックを基準クロックとし、入力信号であるアナログ信号をデジタル変換してデジタル処理を施し、処理結果をアナログ変換して出力するデジタルシステムにおいて、PLL回路が発生するクロックに含まれるジッタの影響を最小限に抑制すること。

【解決手段】遅延器4の遅延時間は、デジタル処理回路3と遅延器4の合計遅延時間がクロックのジッタの周期と等しくなるように調整してある。これによって、基準クロックに含まれるジッタ周期の倍数の時間分だけデジタル処理した信号を遅延させてからアナログ変換するので、入力段のA/D変換器2から出力段のD/A変換器5までの遅延時間をジッタ周期と合致させることができ、出力アナログ信号に対するクロックに含まれるジッタの影響を最小限に抑えることができる。

(もっと読む)

スプレッドスペクトルクロック生成器及びスプレッドスペクトルクロック信号を生成する方法

【課題】スプレッドスペクトルクロック生成器(SSCG)及びスプレッドスペクトルクロック(SSC)信号を生成する方法を提供する。

【解決手段】第1フィードバック信号の平均周波数と受信された比較周波数信号との差に基づくか、第2フィードバック信号と比較周波数信号との総位相変化量に基づいて所定の変調電圧信号を出力する制御部、受信された既存周波数信号及び受信された第2フィードバック信号の機能で第1制御電圧を生成するサブシステムを備えるSSCGである。合算部は、第1制御電圧信号と変調電圧信号とを合算して第2制御電圧信号を生成し、電圧制御オシレータは、第2制御電圧信号に基づいてSSC信号を生成する。

(もっと読む)

水晶発振装置

【課題】 従来の発振器では経時変化により劣化して周波数が変化した場合に、定期的に計測しなおしてゼロ調整しなくてはならなかった。そのため計測の設備を用意し、計測しながら周波数調整を行っていた。

【解決手段】 本発明では、二つの発振器のうち第二発振器は普段電源を入れず劣化させないようにし、第一発振器を常に動作させ、定期的または任意の間隔で第二発振器を動作させて、これを基準として第一発振器の周波数ずれを補正し、安定な周波数を得られる発振器としている。そして第二水晶発振器を動作させていない間にも、制御回路で過去のデータから時間当たりの補正量を算出して、周波数調整を行っている。

(もっと読む)

水晶発振装置

【課題】 従来の発振器では経時変化により劣化して周波数が変化した場合に、定期的に計測しなおしてゼロ調整しなくてはならなかった。そのため計測の設備を用意し、計測しながら周波数調整を行っていた。

【解決手段】 本発明では、二つの発振器のうち第二発振器は水晶振動子の水晶電流を多く流して短期安定度のよい発振器とし、これを基準として水晶電流を少なくして長期安定度の特性の良い第一発振器に位相同期させて、安定な周波数を得られる発振装置としている。

(もっと読む)

1 - 11 / 11

[ Back to top ]