Fターム[5L106BB02]の内容

半導体メモリの信頼性技術 (9,959) | エラーの検出、訂正 (500) | エラー検出 (176) | パリティ (66)

Fターム[5L106BB02]に分類される特許

1 - 20 / 66

メモリコントローラ、半導体記憶システムおよびメモリ制御方法

【課題】パリティデータデータの増大を抑えることができるメモリコントローラを得ること。

【解決手段】各しきい値分布に対して、3ビットのデータが割り当てられ、第1のビットが第1ページのデータを表現し、第2のビットが第2ページのデータを表現し、第3のビットが第3ページのデータを表現する3ビット/セルのメモリセルを有する不揮発性半導体メモリを制御するメモリコントローラであって、不揮発性半導体メモリの第1のメモリ領域に、第1〜第3の3ページ分のデータを書き込む場合に、第1のメモリ領域の各メモリセルに書き込まれるデータの第1のビット及び第2のビットから、隣接するしきい値分布への移動によりエラーとなるビットを抽出して仮想ページを生成する制御部と、仮想ページに対する第1の誤り訂正符号を生成する符号化部と、3ページ分のデータと第1の誤り訂正符号とを不揮発性半導体メモリへ書き込むインターフェイス部とを備える。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

不揮発性半導体メモリ

【課題】ReRAMにおいて、従来よりも高いエラー訂正能力を実現しつつ、パリティデータの増大を抑制する。

【解決手段】実施形態に係る不揮発性半導体メモリは、メモリセルアレイ、並びに、書込回路を有するコード記憶部と、書込データを生成した上で書込回路に書込動作を実行させるエンコーダと、規定回数内の書込動作によってメモリセルアレイに対する書込データの書き込みの成功又は失敗を判定し、失敗の場合、書込データを反転させた新たな書込データを生成した上で書込回路に新たな書込データの書込動作を実行させる書込判定回路と、書込判定回路による判定が失敗であった場合、メモリセルから読み出された読出データを反転させた新たな読出データを生成するスイッチ回路と、メモリセルアレイから読み出された読出データをスイッチ回路を介して入力した上で当該読出データから情報データを復元するデコーダとを備える。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を実現可能な半導体装置を提供する。

【解決手段】例えば、それぞれ独立の内部電源生成回路VGEN1〜VGEN3を持つ3個の不揮発性メモリモジュールFMD1〜FMD3を備える。外部書き込みデータが入力された際には、それを2分割したデータの一方がFMD1のデータ領域DT[1a]に書き込まれ、他方がFMD2のデータ領域DT[1b]に書き込まれる。更に、この2分割したデータによってパリティデータが生成され、それがFMD3のデータ領域PT[1]に書き込まれる。このDT[1a],DT[1b],PT[1]への書き込みは、互いに重複しない期間で行われ、また、各データ領域(例えばDT[1a])に書き込みを行う前後で対応する書き込みスタンプ領域(例えばPS[1a])に識別子が書き込まれる。

(もっと読む)

エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法

【課題】エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法を提供する。

【解決手段】半導体メモリ装置のチップ内部でデータ・スクラビングを行うエラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法であって、該メモリ装置のリフレッシュ方法は、メモリ装置の対応する部分について、スクラビングのない少なくとも1つのリフレッシュを行う段階と、メモリ装置の対応する部分について、スクラビングを有する少なくとも1つのリフレッシュを行う段階と、を含む。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

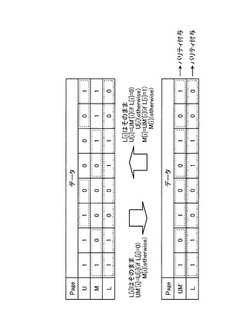

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

半導体記憶装置

【課題】高信頼度、高速アクセス、および動作電流削減を兼ね備えた半導体記憶装置を提供する。

【解決手段】多数決モードにおいて複数個のRAM0−0,1−0,2−0またはRAM0−1,1−1,2−1には同一の書込データが書込まれ、ECCモードにおいて複数個のRAM0−0,1−0,2−0,0−1,1−1,2−1のいずれかにECCコードが付加された書込データが書込まれる。この半導体記憶装置は、多数決モードにおいて、読出時に複数個のRAMに書込まれたデータの多数決結果を出力する多数決回路16と、ECCモードにおいて、書込時に書込データに対するECCコードを生成するECC生成回路12−1〜12−3と、ECCモードにおいて、読出時にRAMに記憶されているECCコードが付加された書込データの誤り訂正を実行するECCエラー訂正回路14−1〜14−3とを備える。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

半導体メモリ装置および復号方法

【課題】復号の処理速度が速いメモリカード3を提供する。

【解決手段】メモリカード3は、1個のメモリセルに記憶する、読み出し単位であるページが異なる3ビットのデータを、8個の閾値電圧分布に基づく確率を用いた反復計算により復号を行うときに、ハードビット読み出しのための7個の基準電圧のそれぞれと、ソフトビット読み出しのための、それぞれの基準電圧よりも低い電圧および高い電圧からなる複数の中間電圧と、からなる7組の電圧セットのうち、読み出すページに属する1ビットデータの読み出しに必要な電圧セットの電圧を選択し、選択した前記電圧セットの電圧を読み出し電圧として前記メモリセルに印加する制御を行うワード線制御部21と、対数尤度比を記憶する対数尤度比テーブル記憶部22と、読み出したデータを対数尤度比を用いてECCフレーム単位で復号をする復号器1と、を有する。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

半導体記憶装置

【課題】セットアップ及びホールド時間のマージンを確保する。

【解決手段】半導体記憶装置1は、第1のクロックを受け、かつデータの入出力を行う第1のバッファ12を有する第1のメモリ10と、データの入出力を行う第2のバッファ22を有する第2のメモリ20とを含む。第1のメモリ10は、第1のクロックを用いて第2のメモリ20に第2のクロックを転送する。第1のバッファ12は、第1のクロックに応答して第2のメモリ20にデータを転送する。第2のバッファ22は、第2のクロックに応答してデータを受ける。

(もっと読む)

半導体回路装置及び誤り検出回路

【課題】データ書き込み時の方向と直交する方向に連続するメモリセルに記憶されたデータ列を該データ列単位で順次読み出すことが可能な半導体回路装置において、前記読み出したデータ列の誤り検出を行うのに好適な半導体回路装置を提供する。

【解決手段】半導体回路装置1の誤り検出回路43を、列誤り検出回路50_0〜50_nと、誤り検出用OR回路51とを含んだ構成とし、各列誤り検出回路において、LCDからのクロック信号LCD_CKに同期してメモリセルアレイ21から行単位に順に読み出される表示用データLCD_RDの、1ライン目の読み出し時において同じ1周期にパリティデータPTDを読み出し、行単位で順次読み出される各ラインにおける列方向に書き込まれた各ビットデータと1つ前の演算結果との排他的論理和演算を順次行い、表示用データCPU_WDに対する最終的な演算結果を誤り検出用OR回路51に出力する構成とした。

(もっと読む)

半導体装置及びその制御方法

【課題】欠陥セルのリフレッシュによる救済制御を簡易にする。

【解決手段】 半導体装置は、第1及び第2のROMと、設定信号に基づいて、入力ノードに時系列に複数回供給される複数の入力アドレスから、前記第1及び第2のROMにそれぞれ記録すべき第1及び第2のアドレスを設定する制御回路と、を備え、前記制御回路は、前記設定信号に基づいて前記入力アドレスを前記第1のアドレスとして設定し、前記第1のアドレス信号が設定された後には、前記設定信号に基づき、且つ、前記設定された第1のアドレスと前記入力アドレスとが予め定めた一部のビットに関して互いに異なる場合に、その時の前記入力アドレスを前記第2のアドレスとして設定する。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの製造方法

【課題】 2ビット不良を2つの単ビット不良に置き換えてエラー訂正することで、半導体メモリの歩留を向上する。

【解決手段】 半導体メモリは、第1および第2データ端子群で受けるリアルデータを記憶する第1および第2リアルメモリセル群と、リアルデータのうち第1データの第1パリティデータを記憶する第1パリティメモリセル群と、リアルデータのうち第1データを除く第2データの第2パリティデータを記憶する第2パリティメモリセル群とを有する。半導体メモリは、割り当て切り替え回路を用いて、第1エラー訂正モード中に、第1データを第1リアルメモリセル群に記憶し、第2データを第2リアルメモリセル群に記憶し、第2エラー訂正モード中に、第1データと割り当てが異なるリアルデータを第1リアルメモリセル群に記憶し、第2データと割り当てが異なるリアルデータを第2リアルメモリセル群に記憶する。

(もっと読む)

誤り訂正符号復号装置及び誤り訂正符号復号方法

【課題】 硬判定復号と軟判定復号の併用により、NANDフラッシュメモリ等の読み出しデータの信頼性を向上させると共に、全体としての処理時間の短縮をはかる。

【解決手段】 ビット当り2値の信号を入力データとして硬判定復号を実行すると共に、該入力データに対してパリティ検査を実行する硬判定復号部11と、ビット当り多値数が2より大きい信号を入力データとして軟判定復号を実行する軟判定復号部13と、硬判定復号部11及び軟判定復号部13の起動を制御する起動制御部14と、硬判定復号部11と軟判定復号部13の各出力信号の一方を選択して出力する出力選択部15とを備え、パリティエラーの個数が許容値内の場合には、硬判定復号部11の復号結果を選択して出力し、パリティエラーの個数が許容値を超えた場合には、軟判定復号部13を起動すると共に軟判定復号結果を選択して出力する。

(もっと読む)

半導体装置

【課題】回路面積を低減出来る半導体装置を提供すること。

【解決手段】半導体装置1は、NAND型フラッシュメモリ2と、NAND型フラッシュメモリ2に入力されるデータ、またはNAND型フラッシュメモリ2から出力されるデータについてECC処理を行うECC部30と、外部との間でデータの授受を行うインターフェース23を有し、NAND型フラッシュメモリ2と外部との間のデータの入出力を司る入出力部3と、NAND型フラッシュメモリ2とECC部30との間の接続と、NAND型フラッシュメモリ2と前記インターフェース23との間の接続とを切り替えるスイッチ5と、NAND型フラッシュメモリ2、入出力部3、及びスイッチ5を制御する制御部4とを具備する。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

半導体記録装置及び半導体記録装置の制御方法

【課題】データ保持性能を改善できる半導体記録装置を提供する。

【解決手段】複数のページによって構成される物理ブロックを複数有するフラッシュメモリ6a〜6eと、フラッシュメモリ6a〜6eに記録するデータを受け付ける外部インターフェイス部1と、データにパリティデータを付加し、第1のECC符号を生成する第1のECC生成部3と、フラッシュメモリ6a〜6eのページに第1のECC符号に基づくデータを記録するデータ書き込み部5a〜5eと、ページに対する第1のECC符号のシンボルの割り当てを制御するページシャフリング部2と、を備え、ページシャフリング部2は、第1のECC符号のシンボルがグループを構成する物理ブロックにおける少なくとも2つのページ番号を有するページに割り当てられるように、第1のECC符号のシンボルの割り当てを制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】ECC動作を消去モードの最初に行うことで、高速読み出し動作可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置10は、データ格納用の不揮発性メモリセルが配列されたメモリ領域(メイン消去ブロック110−2〜110−n)と、メモリ領域が不良領域である場合にメモリ領域と置換される冗長領域(冗長用消去ブロック110−1)と、消去動作を示すコマンドが入力されると、消去動作に先立って前記メモリ領域からデータを読み出し、誤り検出を行い、誤り検出結果に基づいて前記冗長領域へと置換する前記不良領域を検出する制御部(制御部12)と、を備える。

(もっと読む)

1 - 20 / 66

[ Back to top ]