Fターム[5L106DD25]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | 試験装置 (1,037) | 試験結果の解析、後処理 (361)

Fターム[5L106DD25]に分類される特許

1 - 20 / 361

メモリコントローラ

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

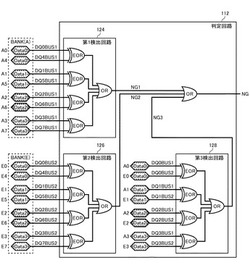

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

集積回路,試験回路,試験装置,及び試験方法

【課題】記憶部と記憶部の試験を行なう試験部とを備える集積回路の回路規模の増大又は製造コストの増加を低減させる。

【解決手段】記憶部3と、供給される一組のアドレス及びデータを含む試験情報に基づいて前記記憶部3に対する書込及び読出試験を行なう試験部4と、を備え、前記試験部4は、前記試験情報に基づき前記記憶部3への書き込みが行なわれた場合に当該書き込みに用いられた第1書込アドレス及びデータを保持する第1保持部5と、前記試験情報に基づく第2書込アドレス及びデータによる前記記憶部3への書き込みと同時に前記記憶部3の第1読出アドレスから第1読出データを読み出す同時読出に用いる前記第1読出アドレスを、前記第1保持部5に保持された前記第1書込アドレスに基づいて生成する第1生成部6と、前記第1読出データの期待値を、前記第1保持部5に保持された前記第1書込データに基づいて生成する第2生成部7と、を備える。

(もっと読む)

半導体メモリ装置及びそのテスト方法

【目的】少ない外部端子によって、半導体メモリ装置に構築されているメモリが故障しているか否かの製品出荷時のテスト及びその故障要因を特定することが可能な半導体メモリ装置及びそのテスト方法を提供することを目的とする。

【構成】半導体メモリ装置に構築されているメモリが読出指令に応答したか否かを判定し、メモリが読出指令に対して非応答であった場合にはメモリから読み出されたメモリデータに代えてエラーコードを外部出力する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

半導体装置

【課題】テスト時間を短縮させる。

【解決手段】フラッシュメモリLSI1は、データを記憶する記憶部であって、予め定められたビット数のデータ領域を複数有するフラッシュメモリ部8と、フラッシュメモリ部8から読み出したデータとデータの期待値とが不一致であるビットを示す不良ビットの数が、予め定められた閾値以下であるか否かを、データ領域ごとに判定する判定回路部10と、判定回路部10が判定した判定結果に応じた出力を出力端子(RB#端子)に出力させるRB制御回路部60と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその試験方法

【課題】電源投入により自走的にメモリセルアレイの動作テストを実行する。

【解決手段】一つの実施形態によれば、不揮発性半導体記憶装置は、不揮発性半導体記憶装置は、ロムヒューズブロックを有するメモリセルアレイ、自走テスト部を有するコントローラ、及びコマンドレジスタを有する。不揮発性半導体記憶装置は、電源投入によりメモリセルアレイの自走テストを実行する。

(もっと読む)

半導体集積回路

【課題】回路規模の増加を抑制しつつ、テスト時間の短縮を図る半導体集積回路を提供する。

【解決手段】BIST回路1は、アドレス信号を生成するアドレス生成回路1bと、書き込みデータ及び書き込みデータに対応する期待値データを生成するデータ生成回路1aと、メモリを制御するチップイネーブル信号生成回路1cと、メモリの書き込み動作及び読み出し動作を制御する制御信号を生成する制御信号生成回路1dとを有する。メモリブロック化回路2は、複数のメモリを有し、アドレス信号から複数のメモリのうちテスト対象となるメモリのアドレスに対応するアドレス入力信号を生成し、且つ、複数のメモリからテスト対象のメモリを選択するメモリ選択信号を生成するアドレス変換回路Aを有し、メモリ選択信号に基づいて、複数のメモリのうちテスト対象のメモリが出力するデータを選択して出力するメモリ出力選択回路DSと、を有する。

(もっと読む)

半導体集積回路

【課題】プロセッサとメモリを備えた半導体集積回路の前記メモリをテストする際に、テスト回路による回路規模の増大を最小限にすることができる半導体集積回路を提供する。

【解決手段】SIMDプロセッサ2が、MBIST・リペアコントロール回路6によりテストされたRAM4の不良の有無と、不良アドレス(不良セル)の位置情報を解析し、メモリコントローラ回路3内部に保持して、通常動作時には、不良メモリの不良アドレスへのアクセス時にはメモリコントローラ回路3がリペア用RAM5へのアクセスするように制御する。

(もっと読む)

半導体記憶装置

【課題】SRAMセルやセンスアンプの駆動トランジスタのしきい値電圧(Vth)を補正することを可能とする技術を提供する。

【解決手段】データを保持するラッチ回路と、データを伝送する信号線とを備える半導体装置を構成する。ラッチ回路は、第1インバータと、第2インバータとを具備する。第1、第2インバータのそれぞれの出力からビット線(BL0、BL1)やセンスアンプ信号線(SA0、SA0B)を経由してGNDへ至る電気的経路を備え、その電気的経路は、第1のトランジスタを備えるものとする。そして、Vt補正モードには、第1インバータまたは第2インバータの一方のHighレベルを供給し他方にLowレベルを供給することで、第1のトランジスタにより電気的経路を導通する。

(もっと読む)

半導体装置

【課題】不良チップの救済効率を向上させ歩留まりを向上させる。

【解決手段】第1半導体チップのメモリセルアレイは、ノーマルセルアレイとスペアセルアレイとを備える。第1不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第1不良アドレスデータを出力する。第1比較回路は、アドレスデータと第1不良アドレスデータとを比較して第1の一致信号を出力する。第2不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第2の不良アドレスデータを出力する。第2比較回路は、アドレスデータと第2の不良アドレスとを比較して第2の一致信号を出力する。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

メモリシステム

【課題】

実施形態は、制御部をテスト可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、前記NAND型フラッシュメモリと前記入出力部との間、および前記NAND型フラッシュメモリと前記入力バッファ部との間に設けられた複数のデータバスと、入力される選択信号に基づいて、所望の前記データバスを選択するスイッチと、前記NAND型フラッシュメモリ、前記入出力部、及び前記スイッチを制御して、前記入力バッファ部から前記NAND型フラッシュメモリにデータを書き込むとき、選択された前記データバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続し、残りのデータバスを介して、前記NAND型フラッシュメモリと前記入力バッファ部との間を接続しない前記選択信号を前記スイッチに出力する制御部とを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

半導体装置、タイミング検出方法及びタイミング調整方法

【課題】半導体装置の設計値に対するタイミング検出、設計値に対するタイミング調整を最適に行う半導体装置、タイミング検出方法及びタイミング調整方法を提供する。

【解決手段】オシレータ回路1−3と、テスト信号の活性化期間内に前記オシレータ回路に対してクロッキング動作を行わせる前記テスト信号を前記オシレータ回路に出力するコマンド回路1−1と、前記オシレータ回路と接続され、前記クロッキング動作によるクロッキング数をカウントするカウンタ回路1−2と、を備える。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

半導体記憶装置

【課題】、半導体記憶装置自身に、適切に自半導体記憶装置に関する装置情報を記憶することができる、半導体記憶装置を提供する。

【解決手段】特定ワード線(1024番目のワード線)上のステータスレジスタ42が設けられていない領域である、8番目〜255番目のビット線と交差する領域に設けられている強誘電体メモリにより生産履歴記憶容量44を構成し、生産履歴記憶容量44に、半導体記憶装置10(半導体チップ20)の生産履歴に関する情報を記憶させている。また、生産履歴記憶容量44への記憶・参照は、主記憶容量40への記憶・参照に使用される通常のコマンドと異なる特殊なコマンドが用いられる。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】サブワード線駆動回路を正確に不良検出する技術を提供する。

【解決手段】サブワード選択線を介して供給されるサブワード選択信号を受けるサブワード線駆動回路のテスト方法において、改良されたFXT出力回路とFXB出力回路により、Hi−Z信号とHi信号をサブワード線駆動回路に供給する技術を含む。

(もっと読む)

1 - 20 / 361

[ Back to top ]