Fターム[5M024CC90]の内容

Fターム[5M024CC90]に分類される特許

1 - 20 / 55

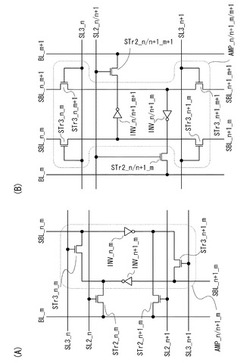

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

WLBIテスト方法

【課題】ビット線を個別に制御することができ、同一センスアンプ列内の隣接ビット線間に“H/L”逆相ストレスパタンを印加できると共に、限定されない種々のストレスパタンをメモリセルに印加できるWLBIテスト方法を提供する。

【解決手段】半導体記憶装置にストレスを印加するのに先立ち、複数のメモリセルを活性化する一方、複数のセンスアンプは非活性状態を維持し、グローバル入出力線GIOB<0>〜<7>、GIOT<0>〜<7>を利用して各ビット線に個別に充電を行う。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】同一ワード線上の各メモリセルの電位を一括で確定する事で、書き込み動作を短縮させることを可能とした半導体メモリ装置を提供する。

【解決手段】1つの電位制御回路に、複数のスイッチング特性を有するトランジスタを接続することで、書き込み電位を一括で確定する。電位を段階的に変化(上昇又は下降)させ続け、推移させながら所望の書き込み電位を確定し、書き込まれたデータに対する読み出しの結果のデータの正誤を常に監視することで、高精度な書き込み動作と高精度な読み出し動作を実現する。また酸化物半導体を用いたトランジスタの良好なスイッチング特性と高い保持特性を利用する。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

半導体装置及び情報処理システム

【課題】FETの閾値電圧の変動に起因するアンプのセンスマージンの低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、信号線(BL)に信号を出力する第1の回路(MC)と、FET(Q1、Q2、Q3)と、信号線に基準電位を与える第2の回路(Q5)を備えている。FETQ1はノードN1の電位と駆動信号SETの電位との間の電位差に応じてゲート容量が制御されるゲーテッドダイオードとして機能し、FETQ2は制御信号TGに応じて信号線とノードN1との間の接続を制御し、FETQ3はゲートがノードN1に接続されノードN1の信号電圧を増幅する。導通状態のFETQ2を非導通に制御した後、駆動信号SETの電位は第1の電位から第2の電位に遷移する。FETQ1の閾値電圧の変動量に対応して少なくとも第1の電位をオフセット制御し、FETQ3のセンス増幅時にFETQ1の閾値電圧の変動を補償する。

(もっと読む)

エッジ・ダミーメモリセル・ブロックを除去した半導体メモリ装置

【課題】エッジ・ダミーメモリセル・ブロックを除去したオープン・ビットライン構造の半導体メモリ装置を提供する。

【解決手段】メモリセル配列を含むメモリセル・ブロックと、一つ以上の第1センスアンプを具備し、それぞれの第1センスアンプは、第1ビットライン、第1相補ビットライン及び第1サイズの第1トランジスタを有する第1増幅回路を具備するエッジ・センスアンプ・ブロックと、一つ以上の第2センスアンプを具備し、それぞれの第2センスアンプは、第2ビットライン、第2相補ビットライン、及び前記第1サイズと互いに異なる第2サイズの第2トランジスタを有する第2増幅回路を具備するセントラル・センスアンプ・ブロックと、エッジ・センスアンプ・ブロックと電気的に連結され、少なくとも1つのキャパシタを含むキャパシタ・ブロックと、を具備する。

(もっと読む)

半導体記憶装置

【課題】センスアンプに用いられる相補のトランジスタの特性変動を均一化させる。

【解決手段】データを記憶するメモリセルMCと、メモリセルMCからの読み出し信号と参照信号との比較結果に基づいて相補的な状態を維持するセンスアンプとが設けられた半導体記憶装置において、センスアンプに入力される読み出し信号と参照信号とをセンスアンプのノードNA、NB間で互いに入れ替える。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ビット線及びセンスアンプが階層化された構成においてメモリセルの読み出し時にリークの温度依存性に起因するセンス動作の不具合を防止し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、複数のメモリセルMCを含むメモリセルアレイ10と、選択されたメモリセルMCの保持情報を伝送する第1のビット線LBLと、第1のビット線LBLの信号電圧を増幅して出力電流に変換するシングルエンド型の第1のセンスアンプ20と、第1のセンスアンプ20を介して第1のビット線LBLと選択的に接続される第2のビット線GBLと、第2のビット線GBLの信号電圧のレベルを判定する第2のセンスアンプ21と、温度の検知結果に応じて各センスアンプ20、21の活性化期間を制御するセンスアンプ制御回路(14、15)を備えて構成される。これにより、メモリセルMCのリークの温度依存性に起因するセンス動作の不具合を防止可能となる。

(もっと読む)

半導体装置

【課題】センスアンプを用いる半導体装置において、オーバードライブ電圧を生成する昇圧回路を設けたことによる消費電力の増加を低減する。

【解決手段】センスアンプを有し外部電源電圧が供給される半導体装置は、センスアンプに接続する駆動信号配線と、外部電源電圧からこの外部電源電圧よりも高い第1の電圧を生成する昇圧回路と、外部電源電圧を降圧して第2の電圧を生成する降圧回路と、を有する。外部アクセスを伴う通常動作時においてセンスアンプにセンス動作をさせる場合に、センス動作の初期には第1の電圧を駆動信号配線に印加しその後は第2の電圧を駆動信号配線に印加し、その一方で、外部アクセスを伴わないリフレッシュ動作時には、昇圧回路の動作を停止させて、センス動作の初期の段階から第2の電圧を駆動信号配線に印加するようにする。

(もっと読む)

半導体記憶装置

【課題】選択信号を印加せずに、メモリセルからデータを読出す。

【解決手段】第1データを保持し第1ワード線により選択される第1素子と、第2データを保持し第1ワード線により選択される第2素子と、第3データを保持し第2ワード線により選択される第3素子と、第4データを保持し第2ワード線により選択される第4素子と、行アドレスを保持する行アドレス保持部を有し、第1行アドレスと行アドレス保持部が出力する第2行アドレスが一致する場合に制御信号を出力する比較部と、行アドレスをデコードして第1又は第2ワード線に選択信号を出力し、制御信号が入力される場合には選択信号の出力を抑止する行アドレスデコーダと、選択信号により第1データ又は第3データを保持する第1の読出保持部と、選択信号により第2データ又は第4データを保持する第2の読出保持部を有する半導体記憶装置が提供される。

(もっと読む)

半導体記憶装置

【課題】データ入出力回路内でリードデータとモード信号との衝突が生じない半導体記憶装置を提供する。

【解決手段】モード信号が設定されるモードレジスタ54と、メモリセルアレイ70から読み出されたリードデータを増幅するデータアンプ64と、データアンプによって増幅されたリードデータが伝送されるデータバス65と、データバス65上の信号を外部に出力するデータ入出力回路100と、モードレジスタ64に設定されたモード信号をデータバス65に送出するモード信号出力回路200とを備える。本発明によれば、モード信号をデータ入出力回路の途中に割り込ませるのではなく、データアンプとデータ入出力回路とを接続するデータバス上に供給していることから、データ入出力回路内でリードデータとモード信号とが衝突することがない。

(もっと読む)

センスアンプ制御回路

【課題】誤動作がなく、かつ、高速動作を可能とする電流センス型センスアンプの制御回路を提供する。

【解決手段】SEB信号の電圧レベルを上げる充電回路(初期電圧設定回路)1と、SEB信号の電圧レベルを下げる放電回路(制御信号レベル調整回路)2と、SEB信号の電圧レベルを下げる速度を調整する放電調整回路(調整回路)3を備えている。放電調整回路3により、SEB信号の電圧レベルを3段階で下げるようにしたため、電流センス期間と電圧センス期間の双方を最適化することができ、センスアンプの誤動作を防止しつつ、高速動作を実現できる。

(もっと読む)

センスアンプ、およびそのセンスアンプを搭載した半導体記憶装置

【課題】少ない付加回路面積、少ない制御信号で、効果的にセンスアンプオフセットを縮小する。

【解決手段】第1入力信号電圧(BT)と第2入力信号電圧(BB)との差に応じて増幅信号を生成する差動増幅回路(2)と、差動増幅回路(2)に接続され、増幅信号を受ける出力回路(3)と、差動増幅回路(2)に接続される負荷(4)とを具備するセンスアンプ(1)を構成する。差動増幅回路(2)は、増幅信号を出力回路に供給する第1出力ノード(N1)と、第1出力ノード(N1)と対称な位置に設けられ、負荷(4)に接続される第2出力ノード(N2)とを備えていることが好ましい。また、出力回路(3)は、増幅信号に基づいて生成される出力信号を出力する出力端を備えていることが好ましい。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】シングルエンド型の複数のセンスアンプ回路を流れる電流を測定し、そのしきい値電圧のばらつきを容易に判別可能な半導体記憶装置とそのテスト方法を提供する。

【解決手段】本発明の半導体記憶装置は、選択されたメモリセルMCから読み出された信号を伝送する第1のビット線LBLと、第1のビット線LBLの信号電圧を増幅して出力電流に変換する増幅素子Q1を含むシングルエンド型の第1のセンスアンプ回路21と、第1のセンスアンプ回路を流れる電流(独立の接地電位VSSLを経由する電流)を、他の回路部分を流れる電流とは独立に測定するテスト動作を制御する制御回路とを備えている。

(もっと読む)

半導体記憶装置

【課題】MOSトランジスタの閾値電圧の製造プロセスの変動や温度依存性によるシングルエンドセンスアンプの特性変動をキャンセルすることができ、以って、センスアンプの動作マージンを向上させることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置において、メモリセルはローカルビット線及びグローバルビット線を介してローカルセンスアンプとグローバルセンスアンプに接続される。ローカルセンスアンプは、メモリセルのデータの読出・書込時に変動するローカルビット線の電位を検出する単一のMOSトランジスタを含むシングルエンド型センスアンプである。MOSトランジスタの閾値電圧はモニタして高レベル書込電圧と低レベル書込電圧を生成し、これらはモニタ結果に基づいて補正・シフトされ、以って、グローバルセンスアンプによるメモリセルの再書込動作を適正に実行する。

(もっと読む)

半導体装置

【課題】 新たなメモリセルの選択方式を導入することによって、上述した諸問題を解決し安価なDRAMを提供することである。さらには、本選択方式は、その他のDRAMセル、あるいはスタティック・ランダムアクセスメモリ(SRAM)の高性能化にも寄与する。

【解決手段】 アレーを構成する行線Xと列線Yの交点にメモリセルMCが接続され、該1個のメモリセルは行線Xと列線Yで制御され、行線Xと列線Yのそれぞれにパルス電圧が印加されることによって該メモリセルMCが選択されてデータ線DLと信号の授受を行う。

(もっと読む)

半導体記憶装置

【課題】ディスターブを抑制し “1”と “0”との信号差を大きくした半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリセル、ビット線、ワード線、ワード線に沿って延伸するソース線を備え、データ“1”を書き込むサイクルにおいて、センスアンプはビット線に第1の電位を印加し、ドライバは選択ワード線および選択ソース線に第2および第3の電位を印加し、第2および第3の電位は第1の電位を基準として多数キャリアと同極性であり、メモリセルへデータ“0”を書き込むサイクルにおいて、センスアンプは選択ビット線に第4の電位を印加し、ドライバは選択ワード線および選択ソース線に第5および第6の電位を印加し、第6の電位は第2および第3の電位よりも第1の電位に近い電位であり、第5の電位は第6の電位を基準として多数キャリアの極性と同極性であり、第4の電位は第6の電位を基準として多数キャリアの極性に対して逆極性である。

(もっと読む)

1 - 20 / 55

[ Back to top ]