Fターム[5M024FF03]の内容

Fターム[5M024FF03]の下位に属するFターム

ブート回路 (17)

Fターム[5M024FF03]に分類される特許

1 - 20 / 123

半導体装置

半導体集積回路

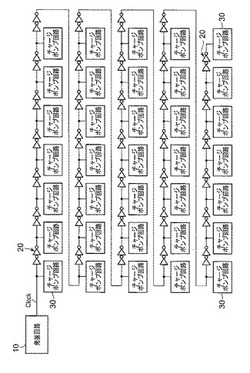

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

半導体装置

【課題】出力端子に接続される内部回路の動作開始を早く行うことができる定電圧発生回路を備えた半導体装置を提供する。

【解決手段】クロック信号VOSCが入力されると、内部の複数のノードにおいてポンピング動作を行い、入力端子に供給される電荷を複数のノードを介して出力端子へと順次転送し、出力端子から出力電圧を発生する昇圧回路20と、出力電圧が予め設定された電圧に達した場合、非活性レベルの検知信号VUPTを出力する電圧検出回路30と、検知信号が活性レベルの場合、クロック信号を昇圧回路へ出力し、検知信号が非活性レベルの場合、クロック信号の昇圧回路への出力を停止するクロック信号制御回路40と、を備え、クロック信号制御回路は、検知信号が非活性レベルであっても、入力される制御信号RESETTのレベルに応じてクロック信号を昇圧回路へ出力する。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードにエントリしている期間中においてもデータ端子のインピーダンス制御を可能とする。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、インピーダンス制御信号ODTを受信する入力バッファ回路72をセルフリフレッシュモード中においても常時活性化させるとともに、セルフリフレッシュモード中においては、内部クロック信号ICLK0に同期してインピーダンス制御信号IODT0をラッチするラッチ回路84をバイパスさせる。これにより、外部クロック信号CKを使用することなく、セルフリフレッシュモード中におけるインピーダンス制御信号ODTの入力が可能となる。

(もっと読む)

半導体装置

【課題】ワード線の活性化電位への立ち上がりの遅れを回避しチップサイズの縮小化、動作速度の高速化に対応可能とする。

【解決手段】メモリセル容量(C)と、前記メモリセル容量及びビット線(BLT)との間に設けられたメモリセルトランジスタ(NM)と、前記メモリセルトランジスタの制御電極に接続されるワード線(SWL)と、前記ワード線を駆動するワードドライバ(SWD)と、を備えた半導体装置であって、前記ワードドライバは、前記ワード線を活性化させる第1の期間、及びそれに続く第2の期間において、それぞれ第1の電源電圧、及び、第2の電源電圧により前記ワード線を駆動し、前記第1の電源電圧は前記第2の電源電圧よりも高い電位である。

(もっと読む)

半導体装置

【課題】リフレッシュ動作時に消費電流量を低減する半導体装置を提供する。

【解決手段】ビット線(BL、/BL)と、電源線(SA電源線)を有し、電源線に供給される電圧を用いてビット線の電位を増幅させるセンスアンプ(SA)と、アクティブコマンドが入力されたことに応じて活性化した時には、アクティブコマンドに対応する電圧供給期間の最初の所定期間にオーバードライブをして電源線に第1の電圧(第1電源線LVOD_kの電圧)を供給して、所定期間後に第1の電圧よりも低い第2の電圧(第2電源線LVARY_kの電圧)を供給し、一方、リフレッシュコマンドが入力されたことに応じて活性化した時には、オーバードライブをすることなくリフレッシュコマンドに対応する電圧供給期間の最初から電源線に第2の電圧を供給する電源電圧発生回路と、を備える。

(もっと読む)

昇圧回路用制御回路及び半導体集積回路装置の動作方法

【課題】ピーク電流を抑制することができる、半導体集積回路装置及び半導体集積回路装置の動作方法を提供すること。

【解決手段】リフレッシュ動作を行うことを示すリフレッシュコマンドの発行を検出し、リフレッシュ検出信号を生成する、リフレッシュコマンド検出回路と、前記リフレッシュ検出信号に基づいて、リフレッシュ動作時に駆動される複数の昇圧回路の動作を制御するための制御信号群を生成する、台数決定回路とを具備する。前記台数決定回路は、前記リフレッシュ検出信号の生成間隔に基づいて、リフレッシュ動作時に駆動される前記昇圧回路の台数を決定し、決定した台数の前記昇圧回路を駆動させる信号群を、前記制御信号群として生成する。

(もっと読む)

ロジックプロセスで埋め込まれたDRAMのためのワード線ドライバ

【課題】慣用のロジックプロセスによる埋込みDRAMセルのデータ保持性能を改善できるワード線ドライバを提供する。

【解決手段】慣用のロジックプロセスによるpチャネルトランジスタ101を含むDRAMセルにアクセスするためのワード線ドライバを提供する。このワード線ドライバは、p型基板の中の深いn型ウェル領域の中に配置したp型ウェル領域に設けたnチャネルトランジスタ313を含む。負極性のブースト電圧供給源から前記p型ウェルおよび前記nチャネルトランジスタのソースに負極性ブースト電圧を供給する。この負極性ブースト電圧は、pチャネルアクセストランジスタのスレッショルド電圧以上の電圧値だけ接地電位よりも低い。深いn型ウェルおよびp型基板は接地電位点に接続する。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路が発生するノイズがセンシティブな回路ブロックに与える影響を低減する。

【解決手段】電源ラインVLに内部電圧V0を供給する内部電圧生成回路1,2を複数個並列に接続し、付加回路3に含まれる複数の回路ブロックのうち、ノイズの影響を受けやすい回路ブロックが動作中ではない場合は、内部電圧V0の低下に応答して全ての内部電圧生成回路1,2を活性化させ、ノイズの影響を受けやすい回路ブロックが動作中である場合は、内部電圧V0が低下しても内部電圧生成回路2のみを活性化させ、内部電圧生成回路1を活性化させない。これにより、内部電圧生成回路の動作に伴う負荷回路3へのノイズの影響を低減させる。

(もっと読む)

半導体装置

【課題】センスアンプSAのオーバードライブ期間を最適化する。

【解決手段】センスアンプSAの電源ノードbにVSS電位を供給するドライバ回路41と、センスアンプSAの電源ノードaにVARY電位及びVOD電位をそれぞれ供給するドライバ回路42,43と、ドライバ回路41〜43の動作を制御するタイミング制御回路50とを備える。タイミング制御回路50は、ドライバ回路43のオン期間を決める遅延回路52を含む。遅延回路52は、遅延量が外部電源電位VDDに依存する遅延回路52bと、遅延量が外部電源電位に依存しない遅延回路52aとを含み、ドライバ回路43のオン期間は、遅延回路52aの遅延量と遅延回路52bの遅延量の和によって決まる。これにより、オーバードライブ期間の長さを外部電源電位VDDのレベルに適度に依存させることができる。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路を活性化させる際又は非活性化させる際における内部電圧の急激な変動を防止する。

【解決手段】外部電圧VDDから生成した内部電圧VPPを内部電源配線110aに供給する内部電圧生成回路110と、内部電圧生成回路110の動作を制御する制御回路300と、前記第1の電圧のレベルを検出する電圧検出回路330とを備える。例えば、制御回路300は、内部電圧生成回路110を活性化させる場合、内部電圧VPPの供給能力を第1の速度で段階的に上昇させ、内部電圧生成回路110を非活性化させる場合、内部電圧VPPの供給能力を第1との速度と異なる第2の速度で段階的に下降させる。これにより、内部電圧生成回路110を活性化/非活性化させる際の内部電圧VPPの大幅な変動をそれぞれ最適に防止することが可能となる。

(もっと読む)

半導体記憶装置

【課題】ネガティブワード線方式の半導体記憶装置において非選択ワード線の電位を安定させる。

【解決手段】少なくとも1つのメモリブロック(60)を備えた半導体記憶装置(50)において、第1の負電位を出力する第1の負電位発生回路(64)と、第2の負電位を出力する第2の負電位発生回路(65)と、メモリブロックにおけるワード線(13)と第1の負電位との間の第1の放電経路(25)と、ワード線(13)と第2の負電位との間の第2の放電経路(21)とを備えている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミスを防ぐことが可能である。

(もっと読む)

セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧印加方法

【課題】内部高電源電圧を利用して希望の動作をうまく行える半導体メモリ装置を提供する。

【解決手段】セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧の印加方法が開示される。

複数のメモリバンクからなるメモリセルアレイを具備した半導体メモリ装置を動作させるために高電源電圧を印加する方法は、半導体メモリ装置の動作モードによって区別され得る。セルフリフレッシュ動作と同一である特定動作モードで外部の高電源電圧を受ける必要なく、内部から生成された高電源電圧を受けてメモリバンク別、またはメモリバンクグループ別にセルフリフレッシュを行う方法によれば、高電源電圧発生器のパンピング効率低下の発生無し、動作に必要な高電源電圧が安定的に印加される。

(もっと読む)

ESD保護回路及び半導体装置

【課題】ESD保護回路に使用するMOSトランジスタのオフリーク電流を低減して、信号端子の端子リーク電流を低減する。

【解決手段】ESD保護回路100は、MOSトランジスタ10(又は20)を備える。MOSトランジスタ10(又は20)は、ドレイン端子とソース端子が信号端子2と電源VDD(又はGND)にそれぞれ接続され、ソース端子に印加されるVDD(又はGND)の電位よりも絶対値が大きく、ゲート端子とソース端子間の制御電圧が逆バイアスとなる電位VH(又はVL)がゲート端子に印加される。

(もっと読む)

半導体装置

【課題】内部電源発生回路から生成される内部電源を受けて安定動作を図りつつ、消費電力を抑制する半導体装置を提供する。

【解決手段】制御回路12、ロウカラムデコーダ13およびセンスアンプ15は、アレイ電圧VddTで駆動する。一方、消費電力の大きいデータパス14は、外部電源電圧VddLで駆動する。そして、レベル変換回路17は、外部電源電圧VddLの電圧レベルをもつアドレス信号またはコマンド信号を受けて、その電圧レベルをアレイ電圧VddTに変換し、制御回路12へ出力する。また、レベル変換回路18は、制御回路12からアレイ電圧VddTの電圧レベルをもつ制御信号を受けて、その電圧レベルを外部電源電圧VddLに変換し、データパス14へ出力する。

(もっと読む)

バックバイアス電圧のリップル・ノイズを減らす半導体メモリ装置及びその駆動方法

【課題】バックバイアス電圧のリップル・ノイズを減らす半導体メモリ装置及びその駆動方法を提供する。

【解決手段】ワードライン駆動回路と遅延ロジック回路とを含み、該ワードライン駆動回路は、サブ・ワードライン・イネーブル信号、第1ワードライン駆動信号及び第2ワードライン駆動信号に応答し、選択されたメモリセルに連結されるサブ・ワードラインを第1電圧にイネーブルさせ、非選択のメモリセルのサブ・ワードラインを第2電圧及び第3電圧にディセーブルさせ、該遅延ロジック回路は、サブ・ワードラインのディセーブル時、第1ワードライン駆動信号の遷移時点を基準にして、サブ・ワードライン・イネーブル信号の遷移時点を可変させ、第3電圧に流入されるサブ・ワードラインのチャージ量より、第2電圧に流入されるサブ・ワードラインのチャージ量が多いように制御する半導体メモリ装置である。

(もっと読む)

昇圧回路、昇圧方法、半導体装置

【課題】負荷電流の変動に応じて出力のリップルを小さく抑える昇圧回路を提供する。

【解決手段】昇圧部(50、58)と、クロック生成部(10、38)と、電流検知部(21)と、クロック制御部(40、16/26)とを具備する。昇圧部(50、58)は、供給される昇圧クロックに基づいて、入力電圧を昇圧して出力する。クロック生成部(10、38)は、昇圧部(50、58)に昇圧クロックを供給する。電流検知部(21)は、昇圧部に供給される電流を検知する。クロック制御部(40、16/26)は、電流検知部(21)が検知した電流量に基づいて、昇圧クロックを制御する。

(もっと読む)

1 - 20 / 123

[ Back to top ]