Fターム[5M024JJ59]の内容

Fターム[5M024JJ59]に分類される特許

1 - 20 / 80

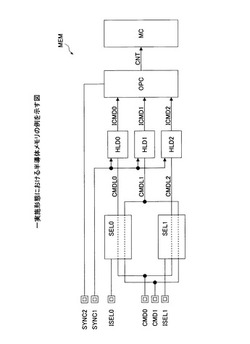

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

半導体装置

【課題】小規模な論理回路によって基準レイテンシとオフセットレイテンシを用いた演算を行う。

【解決手段】例えば、基準レイテンシCLの値を示す複数のビットA0〜A3のそれぞれと、オフセットレイテンシSRLの値を示す複数のビットC0〜C2のそれぞれと、を論理合成して複数の制御信号E0〜E3を生成する論理回路100と、複数の制御信号E0〜E3をデコードして複数の制御信号ULPCL4〜ULPCL15を生成する論理回路200とを備える。本発明によれば、基準レイテンシCLの値とオフセットレイテンシSRLの値をデコードする前に演算していることから、より小規模な論理回路によって調整レイテンシULPCLを算出することが可能となる。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アドレス信号ADD及びコマンド信号CMDに基づいてメモリセルアレイ11を活性化させるアクティブ制御回路230と、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証することによりパリティエラー信号PERRを生成する検証回路90と、パリティエラー信号PERRがフェイルを示した場合、活性化されているメモリセルアレイ11を所定時間経過後に非活性化させるエラー処理回路120を備える。これにより、パリティエラーが発生した場合であっても、既に発行されたコマンドを正しく実行した後にメモリセルアレイを非活性化させることができる。

(もっと読む)

半導体装置

【課題】1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込む。

【解決手段】例えば、モードレジスタ設定信号MRS1を活性化させるコマンドデコーダ82と、モードレジスタ設定信号MRS1を遅延させることによってモードレジスタ設定信号MRS2を生成するレイテンシシフタ83と、データ信号D0がローレベルである場合にはモードレジスタ設定信号MRS2に基づいてモードレジスタ設定信号MRS3を活性化させ、データ信号D0がハイレベルである場合にはモードレジスタ設定信号MRS3を非活性状態に保持する論理ゲート回路G2,G3と、モードレジスタ設定信号MRS3の活性化に応答してモード信号が設定されるモードレジスタ84を備える。これにより、1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込める。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

半導体装置

【課題】外部電圧変動によるコマンドラッチミスの発生を抑制することができる半導体装置を提供する。

【解決手段】半導体装置600は、入力される第1のパルス信号1shot.CMDに由来する第1の入力信号と、入力される第2のパルス信号Out.CLKに由来する第2の入力信号と、が入力されるラッチ回路612と、ラッチ回路の出力を第2のパルス信号に依存するタイミングで後段へ出力する出力回路613と、第2のパルス信号に基づいて、第1の入力信号のパルス幅を第1のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給するか、または、第2の入力信号のパルス幅を第2のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給する前処理回路611とを備える。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードにエントリしている期間中においてもデータ端子のインピーダンス制御を可能とする。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、インピーダンス制御信号ODTを受信する入力バッファ回路72をセルフリフレッシュモード中においても常時活性化させるとともに、セルフリフレッシュモード中においては、内部クロック信号ICLK0に同期してインピーダンス制御信号IODT0をラッチするラッチ回路84をバイパスさせる。これにより、外部クロック信号CKを使用することなく、セルフリフレッシュモード中におけるインピーダンス制御信号ODTの入力が可能となる。

(もっと読む)

半導体装置及びその制御方法並びに情報処理システム

【課題】ギアダウンモードのオン/オフによるラッチタイミング差をなくす。

【解決手段】クロック信号CLK1を分周することによってクロック信号CLK2を生成する分周回路2と、チップ選択信号CS1とクロック信号CLK2を論理合成することによりチップ選択信号CS2を生成する論理回路4と、チップ選択信号CS2に基づいて活性化されコマンド信号CMD1に基づいてコマンド信号CMD2を生成するコマンド生成回路6とを備える。本発明によれば、分周されたクロック信号に同期してコマンド信号のラッチを行うのではなく、分周されたクロック信号に同期してコマンド生成回路を活性化させていることから、分周されていないクロック信号に同期してコマンド信号のラッチ動作を行うことができる。これにより、ギアダウンモードのオン/オフによるラッチタイミングに差が生じなくなる。

(もっと読む)

半導体装置

【課題】レイアウトサイズの増加を避けながら、2つの回路の定期的な動作の時間間隔を互いに独立して設定可能とする。

【解決手段】半導体装置は、セルフリフレッシュコマンドSelfEnableを受けて第1周期のセルフリフレッシュ開始信号SREF_Startを出力し、DLLイネーブルコマンドDLLEnableを受けて第2周期のDLLスタート信号DLL_Startを出力するDLLリフレッシュ制御回路71と、セルフリフレッシュ開始信号SREF_Startに基づいて制御されるリフレッシュ回路53と、DLLスタート信号DLL_Startに基づいて制御されるDLL回路70とを備える。

(もっと読む)

半導体装置

【課題】コマンドに応じて、半導体装置全体ではなく、バンクグループ別にリフレッシュ動作が可能なようにし、リフレッシュ動作を行わないバンクグループでは、読出し・書込みなどの動作が可能な半導体装置を提供すること。

【解決手段】半導体装置は、少なくとも2つ以上のバンクBANK0〜BANK15をそれぞれ含む複数のバンクグループBG0〜BG4と、複数のバンクグループにそれぞれ対応する複数のアドレスカウンタ部110_BG0〜110BG3とを備え、バンクグループリフレッシュコマンドREF_BGが印加されると、選択されたバンクグループのアドレスカウンタ部110_BG0〜110BG3のアドレスカウントによって、選択されたバンクグループのリフレッシュ動作を行うように構成されている。

(もっと読む)

半導体装置

【課題】一の動作の契機を他の動作の契機として利用する場合に、2つの動作が互いに影響し合うことを防止する。

【解決手段】

半導体装置は、制御回路107を備える。制御回路107は、例えば、少なくとも外部及び内部タイマのいずれか一方からコマンドデコーダ109を介して特定信号が供給される度に第1の動作(リフレッシュカウンタ105等)を引き起こし、第1の動作が所定回数に達すると、次に供給される特定信号に応じて、第1の動作に替えて第2の動作(DLLの更新114またはキャリブレーション115)を引き起こす。

(もっと読む)

セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧印加方法

【課題】内部高電源電圧を利用して希望の動作をうまく行える半導体メモリ装置を提供する。

【解決手段】セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧の印加方法が開示される。

複数のメモリバンクからなるメモリセルアレイを具備した半導体メモリ装置を動作させるために高電源電圧を印加する方法は、半導体メモリ装置の動作モードによって区別され得る。セルフリフレッシュ動作と同一である特定動作モードで外部の高電源電圧を受ける必要なく、内部から生成された高電源電圧を受けてメモリバンク別、またはメモリバンクグループ別にセルフリフレッシュを行う方法によれば、高電源電圧発生器のパンピング効率低下の発生無し、動作に必要な高電源電圧が安定的に印加される。

(もっと読む)

半導体メモリ

【課題】 クロック同期式の半導体メモリにおいて、内部回路の動作を必要最小限にすることで消費電流を削減する。

【解決手段】 コマンドバッファは、メモリ動作を指示するコマンド信号を、チップの選択を指示するチップセレクト信号の活性化時に受け付け、内部コマンド信号として出力する。第1クロック発生回路は、チップセレクト信号が供給されたクロックサイクルおよびその次のクロックサイクルに、外部クロック信号に同期して第1内部クロック信号を生成する。コマンドラッチ回路は、第1内部クロック信号に同期して内部コマンド信号を取り込む。

(もっと読む)

付加レイテンシを有する半導体装置

【課題】付加レイテンシを有する半導体装置を提供する。

【解決手段】コマンドを受信し、コマンドが受信された時点から始まる付加レイテンシ区間の終了時点で、対応するメモリアクセス動作を行い、位相制御部及び制御部を具備でき、位相制御部は、クロック信号の位相を制御して位相制御クロック信号を生成でき、制御部は、付加レイテンシ区間のうち所定の時点で、ディスエーブル状態の位相制御部をイネーブルさせる第1論理状態の制御信号を生成して出力できる半導体装置である。

(もっと読む)

半導体メモリおよび半導体メモリの動作方法

【課題】 制御信号生成回路がフリーズしたときに、アクセスサイクル時間を増加することなく制御信号生成回路をリセットする。

【解決手段】 基幹信号生成回路は、アクセスコマンドに応答して基幹信号を活性化し、リセット信号またはハングアップ信号に応答して基幹信号を非活性化する。制御信号生成回路は、基幹信号に応答してメモリコアをアクセスするための制御信号を順次に生成し、制御信号の少なくともいずれかに応答してリセット信号を生成する。ハングアップ信号生成回路は、次のアクセスコマンドに応答してハングアップ信号を生成する。ハングアップ信号を半導体メモリの内部で生成される信号ではなく、半導体メモリの外部から供給されるアクセスコマンドに応答して生成することで、制御信号生成回路がフリーズしたときに、アクセスサイクル時間を増加することなく制御信号生成回路をリセットできる。

(もっと読む)

半導体装置

【課題】ビット線のイコライズトランジスタに高耐圧のトランジスタを用いずに高速にイコライズする半導体装置を提供する。

【解決手段】第1及び第2のビット線と、第1のビット線に一端が接続され第2のビット線に他端が接続されたトランジスタと、上記トランジスタに第1の基板バイアス電圧又は第2の基板バイアス電圧を供給する基板バイアス制御回路と、を備える。上記トランジスタの基板バイアス電位を制御することにより高速にイコライズし、かつ、待機時及び活性化時のリーク電流増加を防ぐ。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム並びにコントローラ

【課題】特に多ビット品においてしばしば生じる実効的なデータ転送レートの低下を防止する。

【解決手段】メモリ回路部110A,110Bに対してそれぞれ割り当てられたデータ入出力端子LDQ,UDQと、メモリ回路部110A,110Bに対して共通に割り当てられたアドレス端子131と、を備える。メモリ回路部110Aは、チップ選択信号CS1Bが活性化されると、メモリ回路部110Bの動作とは無関係にアドレス信号ADDに基づいてデータ入出力端子LDQを介したリード動作又はライト動作を行う。メモリ回路部110Bは、チップ選択信号CS2Bが活性化されると、メモリ回路部110Aの動作とは無関係にアドレス信号ADDに基づいてデータ入出力端子UDQを介したリード動作又はライト動作を行う。これにより、無駄なデータ転送が防止され、実効的なデータ転送レートが高められる。

(もっと読む)

半導体記憶装置及びこれを制御するメモリコントローラ、並びに、情報処理システム

【課題】パワーダウン時において、DLL回路の動作を継続させるファストイグジットモードと、DLL回路の動作を停止させるスローイグジットモードをオンザフライで選択する。

【解決手段】パワーダウンコマンドに応答して所定の内部回路の動作を停止させるパワーダウンコントロール回路100と、パワーダウンコマンドの発行と同時に外部から選択信号A12が入力される外部端子14とを備える。パワーダウンコントロール回路100は、選択信号A12がローレベルである場合にはDLL回路23の動作を停止させ、選択信号A12がハイレベルである場合にはDLL回路23の動作を継続させる。本発明によれば、パワーダウンコマンドと同時に入力される選択信号A12によってオンザフライでモード選択が可能となる。

(もっと読む)

半導体記憶装置

【課題】適切なタイミングで内部でレイテンシを設定する半導体記憶装置を提供する。

【解決手段】トリガ生成回路104は、トリガ信号を出力する。遅延回路110は、トリガ信号を受けて、トリガ信号を遅延させた遅延信号を出力する。クロックカウンタ106は、クロックを受け、トリガ信号が受けてから遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力する。判定回路107は、クロックの数とレイテンシとの対応関係を記憶し、クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する。レイテンシ用レジスタ108は、判定されたレインテンシを保持する。WAIT制御回路109は、レイテンシ用レジスタ108に保持されたレインテンシに基づき、外部にWAIT信号を出力する。

(もっと読む)

1 - 20 / 80

[ Back to top ]