Fターム[5M024KK19]の内容

DRAM (26,723) | 特定の機能を有するメモリ、特殊なメモリ (655) | 特定の機能 (123) | 多値 (12)

Fターム[5M024KK19]に分類される特許

1 - 12 / 12

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

記憶素子の駆動方法及び半導体装置の駆動方法

【課題】記憶素子(DRAM)の保持情報の多値化を簡便に行うこと。

【解決手段】記憶素子(DRAM)が有するトランジスタがオン状態の期間において、当該記憶素子(DRAM)に対して情報の書き込みを行う配線(ビット線)の電位を変動させることで、当該記憶素子(DRAM)が有する容量素子に蓄積される電荷量を制御する。これにより、当該記憶素子(DRAM)を有する半導体装置の構造を複雑化せずとも記憶素子(DRAM)の保持情報を多値化することが可能である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置の駆動方法

【課題】信頼性の高い書き込み動作を高速に行うことのできる半導体装置の駆動方法を提供する。

【解決手段】多値書き込みを行う半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに、書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。書き込みを行いながらビット線の電位を検知することによって、書き込みベリファイ動作を行うことなく、書き込みデータに対応した電位がフローティングゲートに正常に与えられたかを確認することができる。

(もっと読む)

記憶装置、半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのスイッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。

(もっと読む)

2つのゲート用トランジスタを有する多値メモリ記憶装置

本発明は、記憶素子(105)に結合された第1及び第2のノードをそれぞれ有し、互いに並列に配置された第1のゲート用トランジスタ(101)及び第2のゲート用トランジスタ(103)を具える多値メモリセル(111)と、前記第1のゲート用トランジスタ及び第2のゲート用トランジスタのそれぞれの第3のノード及び第4のノードに結合され、前記多値メモリセル(111)の記憶電圧を検出する検出回路(113、115)とを具えるデジタルメモリ装置及びシステム、並びにデジタルメモリ装置の動作方法を提供する。実施例では、第1及び第2のゲート用トランジスタ(101、103)を互いに異なるしきい値電圧レベルで駆動されるように構成する。  (もっと読む)

(もっと読む)

半導体メモリデバイス、電子デバイス、およびその動作方法

【課題】リフレッシュ動作に要する電力を低減する。

【解決手段】半導体メモリデバイスは、トランジスタを有する複数のメモリセルに結合された回路を備えている。当該回路は、当該トランジスタのボディの電位を、当該ボディの荷電状態に応じた程度だけ変化させるように構成されている。当該トランジスタのゲート電極は、非アドレス状態に維持される。

(もっと読む)

開放形ビットライン構造を有するマルチレベル動的メモリ装置及びその駆動方法

【課題】開放形ビットライン構造を有するマルチレベル動的メモリ装置を提供する。

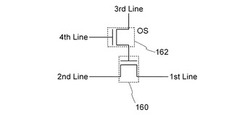

【解決手段】マルチレベル動的メモリ装置は、複数のワードライン、開放形の複数のビットライン、複数のメモリセルであって、前記複数のメモリセルの各メモリセルが、各ワードラインと各ビットラインと接続され、少なくとも2ビット以上のデータを保存する複数のメモリセル、及び複数のセンスアンプ部であって、前記複数のセンスアンプ部の各センスアンプ部が、両側に位置した前記ビットライン間の電圧差を増幅する複数のセンスアンプ部を備える。

(もっと読む)

マルチレベル動的メモリ装置

【課題】マルチレベル動的メモリ装置を提供すること。

【解決手段】マルチレベル動的メモリ装置は、メインビットライン対とサブビットライン対とに分割されたビットライン対と、メインビットライン対間に接続された第1センスアンプと、サブビットライン対との間に接続された第2センスアンプと、メインビットライン対とサブビットライン対との間にそれぞれ交差結合された第1及び第2カップリングキャパシタと、第1及び第2カップリングキャパシタとにそれぞれ並列接続され、制御電圧信号によりキャパシタンスが調節される第1及び第2補正キャパシタと、を備える。

(もっと読む)

メモリ装置の記憶容量を増やす方法

少なくとも2つの記憶素子を有するメモリ装置のメモリ記憶容量を増やす方法において、前記各記憶素子に対してデータ値を対応付ける目的でその公称値を用いることが可能な少なくとも1つの識別可能な物理特性が、各記憶素子に対応付けられる。記憶素子と、任意の時間における当該記憶素子の実際値とに対応付けられた、1つ以上の物理特性の各公称値に関する少なくとも2つの記憶素子の差異が、追加の記憶容量を提供するために用いられる。 (もっと読む)

3値メモリ回路

【課題】1Vの電源下で、H,M,Lレベルの3値の信号をメモリセルに記憶させても適正に読み出しを行うことができるセンスアンプ回路を提供する。

【解決手段】メモリセルに接続されたビット線の電位を増幅する増幅部と、ビット線がリセット電位にされた時に増幅部で増幅された電位を第一のサンプリングパルスにより第一のキャパシタに蓄積する第一のサンプリング保持部と、メモリセルによりビット線が読出し電位にされた時に増幅部で増幅された電位を第二のサンプリングパルスにより第二のキャパシタに蓄積する第二のサンプリング保持部と、第一及び第二のキャパシタに保持されている電位差を検出してラッチするラッチ回路とを有するセンスアンプ回路をHレベル検出用とLレベル検出用に備えた3値メモリ回路。

(もっと読む)

1 - 12 / 12

[ Back to top ]