国際特許分類[G06F11/25]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 待機作動中または遊休時間中の検査によるコンピュータ故障箇所の検出または故障位置の指示,例.始動試験 (1,168) | 論理動作の試験,例.ロジック・アナライザによる (28)

国際特許分類[G06F11/25]に分類される特許

1 - 10 / 28

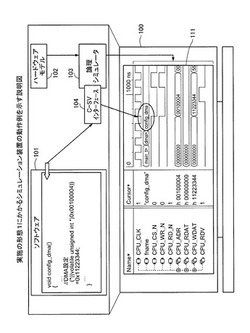

シミュレーション装置、シミュレーション方法、およびシミュレーションプログラム

【課題】ハードウェアとソフトウェアの協調動作のデバッグを効率的に行うこと。

【解決手段】シミュレーション装置100は、ソフトウェア101の実行中に、ハードウェアモデル102にアクセスする特定の関数が実行される場合、論理シミュレータ103側となるC−SVインターフェース104にて特定の関数の関数名を取得する。次に、C−SVインターフェース104は、関数名を記憶領域に格納する。また、論理シミュレータ103も、ハードウェアモデル102のシミュレーションの結果を記憶領域に格納する。波形ビューワ111は、記憶領域に格納されたシミュレーションの結果と関数名とを、時系列で対応付けて表示する。

(もっと読む)

オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法

【課題】 初期導入コストを安く抑えたハードウェアエミュレータを提供し、ハードウェアモデルとハードウェアエミュレータとを容易に接続する技術を提供することを目的とする。

【解決手段】 オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法であって、オープンソースソフトウェアであるQemuを改変することにより、Qemuとハードウェアモデルの接続するTLMインターフェースを介して、ハードウェアモデルに対してデータI/Oを行う手段と、ハードウェアモデルをQemu上でエミュレートしているPCIバスに接続されているPCIデバイスとして見せる手段と、SystemCシミュレータからQemuを起動する手段とを備えたオープンソースソフトウェアのPCエミュレータを実現する。

(もっと読む)

シミュレーション装置、シミュレーション方法およびそのコンピュータ・プログラム

【課題】機能IPの精度の高いシミュレーションを実現することが可能なシミュレーション装置を提供すること。

【解決手段】シミュレーション装置は、ユーザプログラム7を実行することによって機能IPを制御するCPU0(31)と、シミュレータプログラム6を実行することによって機能IPをシミュレートするCPU1(32)と、CPU0(31)およびCPU1(32)によってアクセスされる共有メモリ33とを含む。共有メモリ33には、機能IPの内蔵レジスタに相当する内蔵レジスタ領域がマッピングされており、CPU0(31)は、内蔵レジスタ領域にデータを書き込むことによってCPU1(32)によるシミュレーションを制御する。CPU1(32)は、内蔵レジスタ領域に書き込まれたデータに応じて機能IPのシミュレーションを実行する。したがって、機能IPの精度の高いシミュレーションを実現することが可能となる。

(もっと読む)

活性化パス抽出プログラム,活性化パス抽出装置および活性化パス抽出方法

【課題】実チップの遅延試験の際に信号が伝播した活性化パスを高速に抽出する。

【解決手段】遅延試験の際のテストパターンと実チップのネットリストとに基づき遅延試験のシミュレーションを行なうことにより遅延試験の際に信号値が変化した信号値変化ピンを特定するシミュレーション部11と、このシミュレーション部11によって特定された信号値変化ピンと実チップのネットリストとに基づき信号値変化ピンを辿ることにより活性化パスのトレースを行なうパストレース部12とがそなえられる。

(もっと読む)

再構成可能なプロセッサーのシミュレーション装置及び方法

【課題】 アプリケーションを実行するプロセッサーの性能を評価したりあるいはそのプロセッサーで最適に実行可能なアプリケーションを作成するために使用されるプロセッサーのシミュレーション技術が開示される。

【解決手段】 いくつかの機能ユニットを含んでいる再構成可能プロセッサーのシミュレーション装置はオペランドを生成する機能ユニットとそのオペランドを消耗する機能ユニットの間のルーティング経路をキューで表現してプロセッサーをモデリングする。これらのキューのサイジュは機能ユニットの間のルーティングのディレーに関する情報とスケジューラーから受信したモジューロスケジューリングによる循環ループのステージ情報をもとに決定される。各ルーティングキューの動作に関するホスト向バイナリコードを保存するモデリングコードDBを備えており、バイナリファイルの代わりに対応するホスト向バイナリコードを実行してシミュレーションする。

(もっと読む)

半導体集積回路設計方法

【課題】従来に比べて検証期間を短縮できる半導体集積回路設計方法を提供すること。

【解決手段】処理(ST1)では、半導体集積回路の設計仕様31に対してハードウェア記述言語を用いてRTL(Registor Transfer Level)で記述され、複数のレジスタを表すRTLデータ32を生成する。処理(ST2)では、検証用のデータの事象34に従って、RTLデータ32における複数のレジスタのうちのスキャン対象レジスタ群と、端子情報35(SI、SO、MD)とを用いて、シフトレジスタ構成(SI、SO、MD)となるようにスキャン対象レジスタ群が接続された仮想スキャンチェーンを生成する。処理(ST3)では、検証用のテストパターン33及び事象34に従って、仮想スキャンチェーンに対するシミュレーションを実行する。その実行結果に問題がある場合(ST4−NG)、処理(ST1)を再度実行する。

(もっと読む)

分割搭載した論理回路の論理検証装置

【課題】 大規模な論理を複数のFPGAに搭載して、高速に検証をおこなう場合において、FPGA間に転送サイクル遅れのデータが存在しても、正しい論理動作を実現できる論理検証装置を提供する。

【解決手段】 パラレル−シリアル変換を用い、複数の信号線からの信号を1本の物理線上で送信、受信する時分割転送方法を採用する。このとき、物理線上の信号転送時間をもとに、大規模論理の動作周波数を決める。時分割転送は、クロック信号やリセット信号を時分割転送の対象から除外した、データ信号等を転送対象とし、時分割転送が終了した時に大規模論理のクロックを動作させ、転送したデータを本来の大規模論理のレジスタに反映させる。時分割データ転送処理の開始タイミングおよび終了タイミングの前後には、信号安定化のための保持サイクルが割りあてられ、大規模論理用クロックの立ち上げおよび立ち下げは、両端の保持サイクルに同期して、おこなわれる。

(もっと読む)

論理シミュレータおよび論理検証プログラム

【課題】 検証作業の効率を向上できる論理シミュレータおよび論理検証プログラムを提供する。

【解決手段】 複数の論理回路にそれぞれ対応する複数のシミュレーションデータベースを形成し、複数の論理回路を構成するのに必要な各素子の初期状態設定情報を上記形成した各シミュレーションデータベースに個別に保持する。

(もっと読む)

テスト装置、テスト方法、およびプログラム

【課題】ハードウェアの機能検証の効率を上げて検証期間を短縮すること。

【解決手段】テスト装置1は、オリジナルテストベクタデータを記憶するベクタ記憶部4と、ベクタ記憶部4に記憶されているオリジナルテストベクタデータから、オリジナルテストベクタデータとは異なる生成テストベクタデータを生成するベクタ生成部13と、テストベクタデータを出力する出力部14と、入力信号の誤り発生率を記憶する誤り発生率記憶部4と、乱数データを発生する乱数発生部11と、入力信号の誤り発生率と乱数データとを比較する比較部12とを有する。そして、ベクタ出力部14は、入力信号の誤り発生率より乱数データが小さい場合、生成テストベクタデータを出力し、入力信号の誤り発生率より乱数データが大きい場合、オリジナルテストベクタデータを出力する。

(もっと読む)

データ処理システムにおけるトラフィックフローの統計的表示の使用

【課題】データ処理システムの設計のための検証試験を実施するための装置及び方法が提供される。

【解決手段】該装置は、該データ処理システムの設計の少なくとも一部を表す検証対象システムと、該検証対象システムのインタフェースに接続するため、かつ該検証試験の実施中に該インタフェースを介して該検証対象システムに入力するための信号を生成するためのトランザクタと、を備える。プロファイルストレージは、該インタフェースでの所望のトラフィックフローの統計的表示を提供するプロファイルを保管し、該統計的表示は複数のトラフィック属性に対する統計情報を提供し、また当該トラフィック属性間の少なくとも1つの依存性を特定する。次に、該トランザクタは、生成される該信号が該プロファイルで特定された依存性を考慮するように、生成される該信号を決定するために該プロファイルを参照する。このような機構によって、該トランザクタは、現実のシステムで観察されるであろうトラフィックフローを一層現実に近く再現することが可能になる。

(もっと読む)

1 - 10 / 28

[ Back to top ]