国際特許分類[G06F13/16]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 相互接続または転送のための接続要求 (2,939) | メモリバスに対するアクセスのためのもの (373)

国際特許分類[G06F13/16]の下位に属する分類

優先制御によるもの (24)

国際特許分類[G06F13/16]に分類される特許

1 - 10 / 349

メモリモジュール

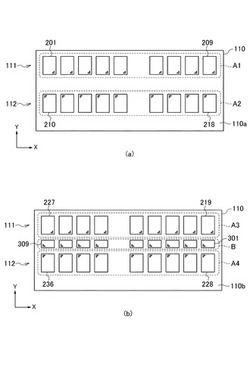

【課題】Load Reduced型のメモリモジュールにおいてメモリデバイスの搭載位置によるデータのスキューを低減する。

【解決手段】データコネクタを有するモジュール基板110と、複数のメモリデバイス201〜236と、データコネクタとメモリデバイスとの間に接続されたデータレジスタバッファ301〜309とを備える。モジュール基板110は、メモリデバイスが搭載されたメモリ搭載領域A1,A2と、平面視でメモリ搭載領域A1,A2に挟まれた位置に定義され、データレジスタバッファが搭載されたレジスタ搭載領域Bとを有する。各メモリデバイスとデータレジスタバッファとの配線距離がほぼ均一になるため、メモリデバイスの搭載位置によるデータのスキューが低減される。

(もっと読む)

メモリモジュール

【課題】Registered型のメモリモジュールにおいてメモリチップに供給するコマンドアドレス信号の信号品質を向上させる。

【解決手段】コマンドアドレス信号CAが供給されるコマンドアドレスコネクタ121を有するモジュール基板510と、メモリデバイス201〜272と、コマンドアドレスレジスタバッファ401,402とを備える。コマンドアドレスレジスタバッファ401は、メモリデバイス201〜236にコマンドアドレス信号CAを供給し、コマンドアドレスレジスタバッファ402は、メモリデバイス237〜272にコマンドアドレス信号CAを供給する。本発明によれば、複数のコマンドアドレスレジスタバッファを用いていることから、メモリチップの数が多い場合であってもモジュール基板上における配線負荷が低減され、その結果、メモリチップに供給するコマンドアドレス信号の信号品質が向上する。

(もっと読む)

ソリッドステートディスク

【課題】異なる動作モードのメモリチップをサポートすることができるソリッドステートディスクを提供すること。

【解決手段】本発明に係るソリッドステートディスクは、メインチップと、第一スイッチと、第二スイッチと、電気抵抗と、前記メインチップに接続される複数のメモリチップと、を備える。メインチップは、メモリチップの動作モードを変えるための第一入出力ピン及び第二入出力ピンを備え、第一スイッチの第一端は、メインチップの第一入出力ピンに接続され、第二スイッチの第一端は、メインチップの第二入出力ピンに接続され、第一スイッチ及び第二スイッチの第二端は、共に電気抵抗を介して接地され、第一スイッチ及び第二スイッチを選択的に開閉させて、メインチップの第一入出力ピン及び第二入出力ピンに入力されるレベル信号を変えると、メインチップは、受信したレベル信号に基づいて、メモリチップの動作モードを変える。

(もっと読む)

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

メモリモジュール及びメモリシステム

【課題】メモリデバイスにおける信号の反射を抑制するメモリモジュール及びこのメモリモジュールを複数備えてジッタを低減できるメモリシステムを提供する。

【解決手段】メモリモジュール1は、外部からアドレス/コマンド信号の入力を受ける外部入力端子3と、外部入力端子3からのアドレス/コマンド信号を受信する複数のメモリデバイス4a〜4hと、を備えている。また、メモリモジュール1は、外部入力端子3から複数のメモリデバイス4a〜4hに向かって2分岐を繰り返して形成された信号線路6を備えている。更に、メモリモジュール1は、信号線路6における2段目以降の分岐点7b〜7g、及び複数のメモリデバイスの入力端子5a〜5hのうち、いずれか一点に接続された終端抵抗9を備えている。

(もっと読む)

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

メモリ制御装置

【課題】メモリ制御装置を提供する。

【解決手段】一次コントローラ及び二次コントローラがフラッシュメモリをアクセスするように制御するメモリ制御装置である。バススイッチは、第1、第2及び第3のシリアル周辺機器インタフェースバスそれぞれを介して、一次コントローラ、二次コントローラ及びフラッシュメモリに接続される。選択ユニットは、第3のシリアル周辺機器インタフェースバスを第1のシリアル周辺機器インタフェースバス及び第2のシリアル周辺機器インタフェースバスのうちいずれか一方に選択的に接続させる。選択ユニットは、バススイッチが第1のシリアル周辺機器インタフェースバスを介して一次コントローラからの第1のアクセス要求を受信した場合に、第3のシリアル周辺機器インタフェースバスを第1のシリアル周辺機器インタフェースバスに接続させる。

(もっと読む)

メモリシステムおよびメモリモジュール

【課題】メモリチップとコントローラとの間において高い信号品質を実現する。

【解決手段】メモリシステムは、コントローラと、第1のデータバスを介してコントローラに接続された第1のメモリモジュールと、第2のデータバスを介してコントローラに接続された第2のメモリモジュールとを備え、第1のメモリモジュールは、第1および第2のメモリチップと、第1のデータバスに接続された第1のデータ端子と、第1のデータ端子を第1および第2のメモリチップのうちのいずれに対して電気的に接続するかを切り替える第1のスイッチ部とを備え、第2のメモリモジュールは、第3および第4のメモリチップと、第2のデータバスに接続された第2のデータ端子と、第2のデータ端子を第3および第4のメモリチップのうちのいずれに対して電気的に接続するかを切り替える第2のスイッチ部と、を備える。

(もっと読む)

フラッシュメモリデバイスを指定する集積回路

【課題】 フラッシュメモリ制御インターフェースを提供する。

【解決手段】 ピンカウントを増やすことなく、マルチデバイスシステムにおいて複数のフラッシュメモリデバイスを制御するインターフェース、装置、および方法を開示する。一実施形態によると、メモリコントローラは、ホストと通信する第1のインターフェースと、複数のフラッシュメモリデバイスと通信する第2のインターフェースとを備えるとしてもよい。第2のインターフェースは、複数のフラッシュメモリデバイスに命令を送信し、デバイス識別情報を受信する設定端子と、複数のフラッシュメモリデバイスにコマンドタイミング信号を送信するコマンド制御端子と、複数のフラッシュメモリデバイスにクロック信号を送信するクロック端子と、複数のフラッシュメモリデバイスから読出コマンドを受信する読出コマンド端子と、複数のフラッシュメモリデバイスとの間でデータの送受信を行う第1の複数のデータ入出力(I/O)端子とを有するとしてもよい。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

1 - 10 / 349

[ Back to top ]