国際特許分類[G06F13/24]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 相互接続または転送のための接続要求 (2,939) | 入力/出力バスに対するアクセスのためのもの (715) | 割込みを用いるもの (144)

国際特許分類[G06F13/24]の下位に属する分類

優先制御によるもの (6)

国際特許分類[G06F13/24]に分類される特許

1 - 10 / 138

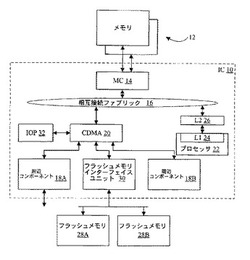

周辺コンポーネントのための高プライオリティコマンドキュー

【課題】集積回路の外部インターフェイスをコントロールする装置を提供する。

【解決手段】一実施形態において、周辺コンポーネントは、周辺インターフェイスを経て転送を行うためにコマンドのセットを記憶するように構成された低プライオリティコマンドキューと、そのインターフェイスを経て転送を行うためにコマンドの第2セットを記憶するように構成された高プライオリティコマンドキューとを備えている。低プライオリティキューにおけるコマンドは、コマンドの第2セットを実行するためにコマンドのセットに割り込むところのポイントを識別する指示を含む。コントロール回路が低プライオリティコマンドキューに結合され、指示に応答して低プライオリティキューからのコマンドの処理に割り込み、高プライオリティコマンドキューからのコマンドを処理する。

(もっと読む)

半導体集積回路および割り込み生成方法

【課題】消費電力を低減すると共に、必要とされる対象処理の遅延を低減することができる半導体集積回路および割り込み生成方法の提供を図る。

【解決手段】レジスタ1を含む回路ブロック100と、前記レジスタの値を読み出して出力するレジスタ値読み出し回路400と、前記レジスタの値を前記レジスタ値読み出し回路から受け取り、予め設定された期待値と前記レジスタ値を比較し、前記比較の結果に基づいて割り込み要求を生成する割り込み生成回路500と、を有する。

(もっと読む)

集積回路装置及びその制御方法

【課題】USBホストコントローラを有する集積回路装置において消費電力を削減する。

【解決手段】集積回路装置は、USBを介してUSBデバイスとの間で通信を行うUSBホストコントローラと、通常動作状態において、前記USBホストコントローラを制御して、前記USBホストコントローラと前記USBデバイスとの間の通信が可能になるようにするための処理を行い、スタンバイ状態において動作を停止する第1プロセッサと、前記スタンバイ状態において、前記USBホストコントローラを制御して、前記通常動作状態に移行するための処理を行い、前記通常動作状態において動作を停止する第2プロセッサとを有する。前記USBホストコントローラと前記USBデバイスとの間で通信可能な状態を維持したまま、前記USBホストコントローラに対する制御が、前記第1プロセッサによる制御と前記第2プロセッサによる制御との間で切り替えられる。

(もっと読む)

ホストコントローラ装置、情報処理装置及びイベント情報出力方法

【課題】省電力化を図りつつシステムメモリへイベント情報を出力することができるホストコントローラ装置、情報処理装置及びイベント情報出力方法を提供すること

【解決手段】本発明にかかるホストコントローラ装置50は、発生したイベント情報をシステムメモリ30へ出力するイベント制御部56と、システムメモリ30に記録されているイベントを実行するCPU20に対して、イベント制御部56からシステムメモリ30へ出力されたイベントの実行を要求する割り込み信号を出力する割り込み制御部54と、を備える。イベント制御部56は、割り込み制御部54がCPU20に対して割り込み信号を出力するタイミングと同期して発生したイベント情報をシステムメモリ30へ出力する。

(もっと読む)

マルチコアLSI

【課題】動作の安定性を向上できるマルチコアLSIを提供する。

【解決手段】このマルチコアLSI1は、第1の共有バスb1に接続された複数のCPU#0,#1と、第2の共有バスb2に接続された1個以上のモジュールm1〜mnと、第1の共有バスb1と第2の共有バスb2との間に接続され、複数のCPU#0,#1のモジュールへのアクセスを調停する共有バス制御部3と、アクセス先のモジュールから、CPU#0,#1のアクセス要求信号に対する応答信号が出力されたか否かを監視するシステムコントローラ9とを備え、システムコントローラ9は、共有バス制御部3から第2の共有バスb2にアクセス要求信号が出力されてから所定時間経過するまでに、アクセス先のモジュールから応答信号が出力されない場合は、共有バス制御部3を介して第1の共有バスb1に疑似応答信号を出力して、アクセス中のCPUの当該アクセスを終了させる。

(もっと読む)

データ転送装置およびフィールド機器

【課題】定期的に到来する所定のデータをDMA転送するデータ転送装置において、システムのパフォーマンスを維持しつつ(CPUの処理能力を奪うことなく)、転送障害が発生した場合に迅速にそれを検出する。

【解決手段】データ転送装置(マイコン110が相当する)の代表的な構成は、定期的に到来する所定のデータ(物理量データ)の転送要求に基づいてそのデータを転送するDMAコントローラ116と、その転送要求に基づいて時間の経過を計測するデータ転送監視回路120内のタイマと、タイマのタイムアウトを検出するタイムアウト検出回路とを備え、データ転送が完了するまでの時間を監視し、その時間内にデータ全体の転送が完了しなければ、タイムアウトが発生するので、転送障害が発生したものとしてエラーを出すようにした。

(もっと読む)

マスタデバイスおよびバスシステム

【課題】CPUの負担を抑えながら、簡単な構成でスレーブデバイスの割り込み要求を監視することができるマスタデバイスを実現する。

【解決手段】本発明に係るマスタデバイス3は、I2Cバスを介してスレーブデバイス2a〜2eに接続され、各スレーブデバイス2a〜2eに割り当てられたデバイスアドレスを指定することで各スレーブデバイス2a〜2eとの通信を行い、スレーブデバイス2a〜2eのうち、割り込み機能を有するスレーブデバイス2a、2b、2d、2eから、マスタデバイス3およびスレーブデバイス2a〜2eを制御するCPU4への割り込み要求を周期的に監視する割り込み監視回路31を備える。

(もっと読む)

データ転送システム及びデータ転送方法

【課題】演算装置から周辺装置へのアクセス時間及びアクセス回数を削減し、消費電力を低減できるデータ転送システムを提供する。

【解決手段】周辺装置4は、演算装置1に割込要求信号を送信する前に、周辺装置4のレジスタセット4r内のデータを主記憶装置2にDMA(Direct Memory Access)転送する。演算装置1は、割込要求信号に応答して、周辺装置4にアクセスすることなく、主記憶装置2にDMA転送されたレジスタセット4r内のデータを読み出す。

(もっと読む)

情報処理装置

【課題】割込み信号にマスクをする際に、システム性能への影響が少なく、パフォーマンスを低下させない省電力機能を備えた情報処理装置を提供する。

【解決手段】所定の省電力モードに移行した状態のCPU120を省電力モードから復帰させる復帰割込み信号222の出力を制御する復帰割込み制御部200を備え、復帰割込み制御部200内の割込みマスク回路220は、CPU120が省電力モードであることを示す省電力モードステータス信号221によりマスクを有効とし、復帰割込み信号222によりマスクを解除する。これにより、マスクの有効、無効(解除)の設定に関してCPU120は操作を行う必要がなく、システムバス121を使用しないため、システム性能への影響が少なく、パフォーマンスを低下させずに、従来よりもCPU120が省電力モードである時間を長くすることができ、消費電力を抑制することができる。

(もっと読む)

マイクロプロセッサ

【課題】書き換え不能なメモリに格納した割り込み処理プログラムを変更できることを目的とする。

【解決手段】複数種類の割り込みで処理する複数のプログラムのアドレスをベクタ毎に格納した第1割り込みベクタテーブルと、第1割り込みベクタテーブルの各ベクタの示すアドレスに処理プログラムを格納する領域とを第1メモリ13に設け、第1割り込みベクタテーブルと同一内容の第2割り込みベクタテーブルを第2メモリ14に設け、第1割り込みベクタテーブルをアクセスするアドレスを第2割り込みベクタテーブルをアクセスするアドレスに変換するアドレス変換手段22を有し、外部機器30から供給される命令により、第2割り込みベクタテーブルの任意ベクタのアドレスと任意ベクタの示すアドレスに格納する処理プログラムとを第2メモリ14に書き込む書き込み手段43を有する。

(もっと読む)

1 - 10 / 138

[ Back to top ]