国際特許分類[G06F7/72]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915) | デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35) | 剰余計算を用いるもの (27)

国際特許分類[G06F7/72]に分類される特許

1 - 10 / 27

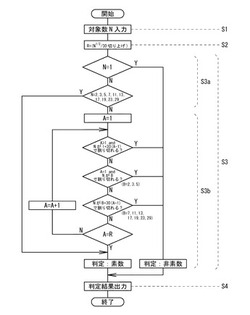

素数判定方法、素数判定装置および素数判定プログラム

【課題】 所定の範囲の既知の素数のみに基づき、大きな対象数についても判定可能な素数判定方法、素数判定装置および素数判定プログラムを提供する。

【解決手段】 対象数N(Nは正の整数)が素数であるか否かを判定する素数判定方法であって、対象数Nの入力を受け付ける入力受付過程と、対象数Nを除する除数の範囲を定める範囲規定過程と、対象数Nを除数で除して、対象数Nが素数であるか否かを判定する素数判定過程と、対象数Nが素数であるか否かの結果を出力する結果出力過程と、を備え、範囲規定過程は、小さいほうからP(Pは2以上の整数)個の素数を掛け合わせた数を素数階乗数MPとして、N1/2/MPの小数点以下を切り上げた規定数Rを算出するものであり、素数判定過程は、整数を1からMP列に並べた配列において、第1行の素数およびR≧2なら第2行から第R行までの第1列およびMPを構成する素数を除いた素数列の数を除数とする。

(もっと読む)

モンゴメリ乗算回路、RSA暗号回路、及び、ICカード

【課題】 回路規模及び消費電力を増大させることなく外部からの消費電力解析が困難なセキュリティ性の高いモンゴメリ乗算回路を提供する。

【解決手段】 モンゴメリ乗算回路1は、メモリ回路11、算術回路10、及び、メモリ回路11と算術回路10間のデータの入出力を所定のアルゴリズムに基づいて制御してモンゴメリ乗算を実現する制御回路12を備えて構成され、制御回路12が、アルゴリズムを2以上有し、2以上のアルゴリズムの内の1つをランダムに選択して、選択した1つのアルゴリズムに基づいてモンゴメリ乗算の実行に係る制御を行う。

(もっと読む)

逆元演算装置および逆元演算プログラム

【課題】有限体の逆元を演算する逆元演算装置に関し,内部変数バッファオーバフローを発生させずに有限体の逆元演算を行うことが可能となる技術を提供する。

【解決手段】逆元演算装置10において,入力部11は,逆元を求める値Xと有限体の法Pとを入力し,中間変数A,B,α,βの設定を行う。条件付中間変数交換部13は,条件に応じて,A−B間,α−β間での値の交換,A−B間,α−β間での減算処理を行う。法符号調整部14は,αの正負に応じて中間法変数P’に−PまたはPを設定する。条件付法加算・シフト部15は,αが奇数である場合にαにP’を加算し,Aおよびαの値を1/2する。変換終了判定部16は,Aの値が1になれば中間変数変換部12による処理の終了を判定する。中間変数符号調整部17は,αが負である場合にαにPを加算する。出力部18は,最終的なαの値を求められた逆元として出力する。

(もっと読む)

データ処理装置

【課題】剰余乗算器の演算ビット数の2倍を超えるビット数のデータに対する剰余乗算の演算効率を向上させることができるデータ処理装置を提供する。

【解決手段】演算部(310)により剰余乗算の演算処理を再帰的に複数回繰り返してwビットの剰余乗算の剰余と商から、2wビットの剰余乗算の商と剰余を計算するとき、先の剰余乗算の演算処理で求めたwビットの剰余乗算の剰余と商を、次の剰余乗算の演算処理に振り分ける制御を制御部(320)が行う。これにより、先の剰余乗算の演算処理がwビットの剰余乗算の剰余だけを求める演算アルゴリズムに比べ、再帰的に行われる後の演算に必要な前の演算処理の商を新たに演算することを要しない。剰余乗算ユニットの演算ビット数の2の倍数のビット数のデータに対する剰余乗算の演算効率を向上させることができる。

(もっと読む)

多倍長演算装置

【課題】楕円曲線暗号等に必要な種々の多倍長演算を高速に実行することが可能な多倍長演算装置を提供する。

【解決手段】演算対象となるnワード長の整数や演算結果等を一時的に記憶するための2個のデュアルポートメモリ41、42からなるメモリ部40と、ワード単位で加算及び乗算を含む2以上の種類の演算を実行し、1ワード長の演算結果を出力する演算部20と、メモリ部40から演算部20に最大3つの1ワードデータを供給すると同時に、演算部20からの1ワード長の演算結果をメモリ部40に格納するメモリ入出力部30と、演算部20及びメモリ入出力部30を制御することにより、演算部20にnワード長の加算剰余及びモンゴメリリダクションのいずれかの演算を実行させる制御を行う制御部10とを備える。

(もっと読む)

乗算装置及びプログラム

【課題】処理単位gが大きい場合に、小さいメモリサイズで高速に乗算を実行する。

【解決手段】乗算装置10では、入出力部12が各入力値A(x),B(x),F(x)を入力し、乗算装置制御部13が入力値B(x)(=x(s-1)gBs-1(x)+x(s-2)gBs-2(x)+…+xigBi(x)+…+xgB1(x)+B0(x))を処理単位g毎に区切ってs個の値Bs-1(x),…,B0(x)を作成し、Mテーブル作成部14が、値Bi(x)の順番i毎のM[i]=A(x)xig mod F(x)の計算結果からなるMテーブルを作成する。Tテーブル作成部15は、Mテーブルを参照し、順番i毎のT[i]=M[i]Bi(x) mod F(x)の計算結果からなるTテーブルを作成する。乗算実行部16は、Tテーブルの計算結果T[s−1],…,T[0]の総和を計算し、乗算結果P(x)=A(x)B(x) mod F(x)として出力する。

(もっと読む)

モントゴメリー乗算に基づくモジュラ乗算及び累乗の改善された装置と方法

【課題】モントゴメリー・モジュラ乗算を実行する、改良された小型電子論理演算装置を提供する。

【解決手段】ρ(A・B)Nのモントゴメリー・モジュラ乗算を実行するものであって、ここでρ(A・B)Nは A・B・I mod N にモジュラ演算上の合同であり、I・2n≡1 mod N であり、A、B及びNはnビット長オペランドであり、Nは奇数であり、該装置は、第一及び第二の主メモリ・レジスタであって、各レジスタはnビット長オペランドを保持し、それぞれ、乗数B、法Nを格納するように適合せしめられたものと、第一の値を第二の値によって、及び第三の値を第四の値によって、同時に乗算し、両方の結果を合計するデバイスであって、該デバイスへの入来ビットとしての予想Y0ビットを出力するための一つの桁上げ保存加算器を有するものと、該桁上げ保存加算器から出力される最下位kビットがゼロとなるようにY0を決定するY0センスユニットと、を具備する。

(もっと読む)

多項式乗算装置、多項式乗算方法及びプログラム

【課題】多項式間の乗算結果を利用して他の多項式間の乗算を行う多項式乗算を、少ないロード回数で実現する。

【解決手段】まず、多項式A(α)の係数系列をレジスタに格納する。次に、或る整数i≧2に対してW(α)=t0+t1・α+…+ti−1・αi−1で表現可能な0及び1を除くすべての多項式W(α)について、それぞれ、多項式W(α)・A(α)の係数系列を生成する。次に、多項式αi−1・A(α)の係数系列の各係数を1次数分だけ高次数側へシフトさせ、そのシフト結果である係数系列を、多項式αi・A(α)の係数系列としてレジスタに格納する。そして、多項式αi・A(α)の係数系列を継続的にレジスタに保持した状態で、W(α)=t0+t1・α+…+ti・αiで表現可能なαiを除くすべての多項式W(α)について、多項式W(α)・A(α)の係数系列が算出されるまで二倍算過程と加算過程と、を交互に実行する。

(もっと読む)

改善されたモジュラー減少演算子

【課題】改善されたモジュラー減少演算子を提供する。

【解決手段】本発明は改善されたモジュラー減少装置に関する。該モジュラー減少装置は、4以上の高い記数法の底rを用いたモンゴメリー乗算プロセスの変形を使用する、乗算器(12)を含む。それはとりわけ非対称の暗号法に用いられる計算要素に適用される。

(もっと読む)

剰余演算装置及び剰余演算方法

【課題】剰余演算を行って暗号アルゴリズムを処理する暗号処理回路において、FPGAの機能拡張に適応した回路構成及び処理方式を採ることで、より少ない回路リソースでの高速動作を可能とし、さらに、回路の汎用性を高めることを目的とする。

【解決手段】被乗数をA、乗数をB、法をM、中間値をQとし、A及びBの乗算結果とM及びQの乗算結果と中間結果Sとの加算結果に基づいて、モンゴメリ乗算による剰余演算を行うモンゴメリ乗算回路201において、演算回路A301及び演算回路D601は、所定の動作周波数clk1xの2倍の動作周波数clk2xにて、A及びBの乗算処理とM及びQの乗算処理とを行う。演算回路B401及び演算回路C501は、clk1xにて、上記2つの乗算処理の結果とSとの加算処理を行う。演算回路C501は、その加算処理の結果に基づいて、モンゴメリ乗算による剰余演算を行う。

(もっと読む)

1 - 10 / 27

[ Back to top ]