国際特許分類[G06G7/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | アナログ計算機 (66) | 計算動作が電気的または磁気的量を変化させることにより行われる装置 (60) | 特定のプロセス,システムまたは装置のためのアナログ計算機,例.シミュレータ (18) | 生体のためのもの,例.神経系統用 (13)

国際特許分類[G06G7/60]に分類される特許

1 - 10 / 13

データ処理のための装置および方法

【課題】大容量コンデンサ素子のため、シリコン表面を実質的に占有してしまうことのないスパイキングニューロンを提供する。

【解決手段】複数のスパイキングニューロン1081...108Nが、受信パルスを蓄積する積分器1091...109Nと、蓄積値に応じてパルスを放出する放電器1141...108Nとを備えるニューロンと、2つの面104、106を有するシリコンの支持体102、103、105とを備え、ニューロン1081...108Nは1つの面上に実装し、積分器1091...109Nは、支持体の2つの表面104、106の間にもうけられた金属ビア1101...110Nを備え、金属ビア1101...110Nは、シリコンの支持体とともにコンデンサを形成して、その電位から蓄積値を形成し、受信したパルスの値の蓄積に応じて放電パルスを放出する。

(もっと読む)

統合発火型電子ニューロン、方法およびプログラム

【課題】 統合発火型電子ニューロンを提供する。

【解決手段】 外部スパイク信号の受信に応じて、外部スパイク信号に基づいて電子ニューロンのデジタル膜電位が更新される。膜電位は漏れ率に基づいて減衰される。膜電位がしきい値を超えたことに応じて、スパイク信号が生成される。

(もっと読む)

相変化メモリを用いたスパイク・タイミング依存可塑性を有する電子学習シナプス

【課題】 人工シナプスにおいてスパイク依存可塑性を発生させるためのシステム、方法及びコンピュータ・プログラムを提供すること。

【解決手段】 1つの実施形態によれば、人工ニューロンにおいてスパイク依存可塑性を発生させるための方法は、第1のニューロンにおいて、第1のニューロンに対する総積分入力が第1の所定の閾値を超えたときに、シナプス前スパイク・イベントを生成するステップを含む。第2のニューロンにおいて、第2のニューロンに対する総積分入力が第2の所定の閾値を超えたときに、シナプス後スパイク・イベントが生成される。シナプス前スパイク・イベント後に、第1のパルスが、相変化メモリ素子を有するシナプスのシナプス前ノードに印加される。シナプス後スパイク・イベント後に、第2の変動パルスがシナプスのシナプス後ノードに印加され、シナプスを通る電流は、第1のパルスの時点における第2の変動パルスの状態の関数である。

(もっと読む)

メモリ・スイッチング素子を用いたスパイク・タイミング依存可塑性を有する電子学習シナプス

【課題】 人工シナプスにおいてスパイク依存可塑性を発生させるためのシステム、方法及びコンピュータ・プログラムを提供すること。

【解決手段】 1つの実施形態によれば、方法は、電子部品内でシナプス前スパイクを受信することと、電子部品内でシナプス後スパイクを受信することと、シナプス前スパイクに応答して、受信したシナプス前スパイクの所定時間後に生じるシナプス前パルスを生成することと、シナプス後スパイクに応答して、ベースライン値から開始し、シナプス後スパイクから第1の時間後に第1の電圧値に達し、その後、シナプス後スパイクから第2の時間後に第2の電圧値に達し、その後、シナプス後スパイクから第3の時間後にベースライン電圧に復帰するシナプス後パルスを生成することと、生成されたシナプス前パルスを、整流素子に直列接続した単極性の二端子型双安定デバイスを含むシナプス・デバイスのシナプス前ノードに印加することと、生成されたシナプス後パルスをシナプス・デバイスのシナプス後ノードに印加することとを含み、シナプス・デバイスはそのシナプス前及びシナプス後ノードに印加された入力電圧の値に基づいて第1の導電状態から第2の導電状態に変化し、シナプス前及びシナプス後パルスが印加された後の、結果として生じるシナプス・デバイスのコンダクタンスの状態は、受信したシナプス前スパイクのシナプス後スパイクに対する相対的タイミングに依存する。

(もっと読む)

情報処理装置及びこれを用いたニューラルネットワーク回路

【課題】シナプス結合強度を抵抗変化型メモリ素子の抵抗値を用いて表わすことにより、LSIチップ上の専有面積を増大させることなく、シナプス結合強度をアナログ量として記憶することができる情報処理装置を提供する。

【解決手段】本発明の情報処理装置100は、少なくとも1つのシナプス回路102を備え、シナプス回路102は、電圧パルスの印加により可逆的に変化する抵抗変化型メモリ素子24と、異なるタイミングで入力される2つのスパイクパルス間における入力タイミングのずれに応じて予め設定された非線形電圧波形を表わす関数を用いた演算を実行するSTDP部25とを有する。STDP部25は、2つのスパイクパルスが入力された場合に、それらの入力タイミングのずれに対する演算を実行し、その演算の結果に基づいて抵抗変化型メモリ素子24に印加される電圧パルスを設定する。

(もっと読む)

ニューロモーフィック回路

本発明の実施形態は、2つ以上の内部ニューロン計算ユニットを含むニューロモーフィック回路に向けられている。各内部ニューロン計算ユニットは、同期信号を受信するための同期信号入力と、入力信号を受信するための少なくとも1つの入力と、出力信号を送信するための少なくとも1つの出力を備える。メムリスティブシナプスは、第1の組をなす1つ以上の内部ニューロンからの出力信号を伝送する出力信号線を、第2の組をなす1つ以上の内部ニューロンに信号を伝送する入力信号線に接続する。  (もっと読む)

(もっと読む)

LSIチップ及び演算処理システム

【課題】 LSIチップに内蔵するメモリ回路ブロックのメモリサイズを超える2次元データに対する演算処理を効率的に実行可能な技術を提供する。

【解決手段】 2次元の対象データと2次元のカーネルとの畳み込み演算を行うLSIチップであって、前記対象データを保持する対象データメモリ10と、前記カーネルを保持するカーネルメモリ11と、前記対象データと、前記カーネルと、に基づいて畳み込み演算処理を行う演算回路16と、前記対象データを外部のLSIチップと入出力する入出力配線と、を備え、前記演算回路16は、前記演算回路における演算において必要な対象データであって、当該LSIチップに備えられた前記対象データメモリ10に存在しないデータは、前記入出力配線を介して、前記外部のLSIチップに備えられた前記対象データメモリから入力することを特徴とする。

(もっと読む)

演算装置

【課題】 複数の被演算値の積和演算を効率的に実行する。

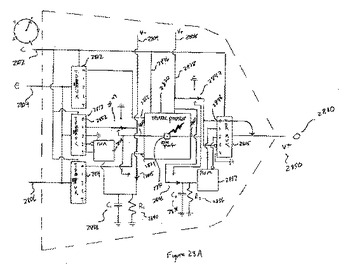

【解決手段】 演算装置に、電圧値で表された被演算値の乗算と累算を含む積和演算処理を実行する積和回路アレイ1と、それぞれ所定の電圧値を設定する電圧設定回路ブロック2、3と、積和回路アレイ1に電圧値の組み合わせを切り替え入力する入力回路ブロック5と、電圧設定回路ブロック2、3が設定する電圧値を、入力回路ブロック5に入力するための配線の接続を切り替えるスイッチ回路ブロック4と、被演算値のアドレスを被演算値の降順または昇順にソートするソーティング回路7と、アドレスをデコードしてスイッチ回路ブロック4に入力するデコーダ8と、積和回路アレイ1による演算結果をディジタル出力する出力回路ブロック6とを備える。

(もっと読む)

協同現象を示す細胞又は細胞群を用いた情報処理システム

【課題】協同現象を示す細胞内又は細胞間の相互作用を利用して既存のデジタル計算機等による情報処理方式とは全く異なる新規な情報処理方式で実行される情報処理システムを提供する。

【解決手段】協同現象を示す細胞である真性粘菌15を素子として用い、障壁部12内に収容された真性粘菌15の変形状態をビデオカメラによりリアルタイムで監視する。そして、その真性粘菌15の変形状態に応じて、プロジェクタにより、真性粘菌15の変形状態を統御する光を所定の照射パターンで照射する。これにより、真性粘菌15の変形状態に応じて光の照射パターンが変わり、その光の照射パターンによってさらに真性粘菌15が変形する、というフィードバックループの過程で、真性粘菌15を変形させることができる。そして、真性粘菌15の自発的なゆらぎを伴う活動により、システムが複数の定常状態のうちの特定の定常状態の間で連鎖的な遷移を繰り返す。

(もっと読む)

半導体装置

【課題】 神経回路コンピュータや多値論理集積回路等の高機能半導体集積回路装置を提供するものである。

【解決手段】 ゲート電極とソース電極とドレイン電極と基盤電極とを有するMOSトランジスタと、複数の抵抗回路とを有し、該ゲート電極に該複数の抵抗回路の出力電極を接続し、前記複数の抵抗回路の入力電極を前記MOSトランジスタの制御用の入力電極とすることである。

(もっと読む)

1 - 10 / 13

[ Back to top ]