国際特許分類[G11C11/404]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | リフレッシングまたは電荷再生,すなわちダイナミック・セル (3,594) | 多数のメモリセルに共通な電荷再生,すなわち外部リフレッシュをもつもの (416) | 1つのセル当り,1つの電荷転送ゲート,例.MOSトランジスタ,をもつもの (92)

国際特許分類[G11C11/404]に分類される特許

1 - 10 / 92

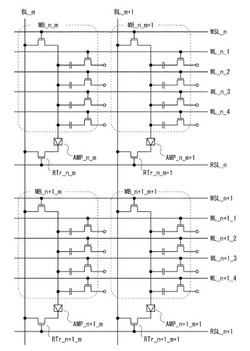

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置

【課題】フローティングボディにデータを記憶するメモリセルを備えた半導体装置において、トリガ素子となる能動素子を設けなくともメモリセルの導通、非導通状態を確実に制御する。

【解決手段】ビット線BLと、ワード線WLと、第1の端子がビット線に接続され、第2の端子がワード線に接続されたメモリセル66と、メモリセルに対するデータの書込み時に、書込みデータの如何に係わらず、ビット線とワード線を選択し、メモリセルを導通させた後、ビット線の電圧レベルを書込みデータに応じた電圧レベルに設定し、メモリセルにデータを書込む制御回路を備える。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体装置

【課題】電流値変化型メモリセルの読み出し動作時に、ビット線電位を低電圧化しても十分な動作マージンを確保可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、電流値変化型メモリセルMCと、ビット線BLと、トランジスタQ1〜Q4からなるセンスアンプSAを備えている。電荷転送ゲートであるトランジスタQ1は転送制御電圧である電位V1に応じてビット線BLとセンスノードNSとの間の接続を制御し、トランジスタQ2はセンスノードNSの信号を増幅する。トランジスタQ3は電位V2をセンスノードに供給し、トランジスタQ4は電位V3をビット線に供給し、ともにプリチャージ制御信号PCに応じて制御される。電位V2を電位V3より高く設定し、電位V1からトランジスタQ1の閾値電圧Vt1を引いた所定電位が電位V3より低く、かつ低電位より高くなるように設定することで、読み出し動作の動作マージンが向上する。

(もっと読む)

データ感知のための半導体メモリ装置

【課題】半導体メモリ装置の低電源電圧におけるデータ感知マージンを高める。

【解決手段】対をなすビットラインBLとビットラインバーBLBに各々データを保存するメモリセル20と、メモリセルと類似の構造を有し、基準電圧を提供する基準セル21が接続されて互いに相補的に動作し、ビットラインとビットラインバーは、プリチャージモードにおいて電源電圧または接地電圧レベルにチャージされ、メモリセルと基準セルのプレートラインは分離し、メモリセルのプレート電圧VPは固定された電圧レベルを維持し、基準セルのプレート電圧VPrefは、アクティブモードで電圧レベルが変動されて容量性カップリングを誘導する。

(もっと読む)

1 - 10 / 92

[ Back to top ]